Nota do Editor: Em projetos modernos de alta velocidade, analisar separadamente a integridade do sinal, a integridade da energia e a EMC não é suficiente; uma abordagem holística é essencial para um design bem-sucedido.

Questão de base: Quando os sinais atravessam áreas de segmentação entre planos de referência adjacentes em uma camada, muitas vezes surgem discussões sobre a integridade do sinal. Alguns argumentam que os sinais não devem cruzar a segmentação, pois isso pode aumentar os problemas de diafonia e EMC, enquanto outros sugerem que, com um design cuidadoso do empilhamento de camadas e da largura das lacunas de segmentação nos planos de energia/terra, não deve haver problema. Então, qual é a abordagem certa? Claro, a melhor resposta é “depende!” Este artigo explora o cenário quando os sinais passam por planos segmentados.

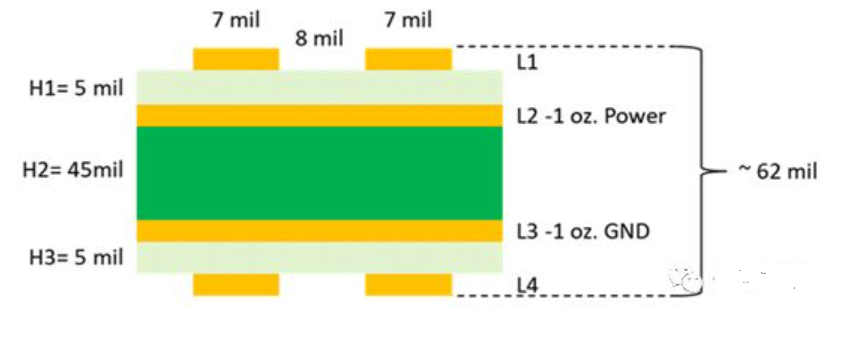

Primeiro, vamos considerar um típico PCB de quatro camadas empilhamento com espessura total de 62 mils. A camada superficial é a camada de sinal, enquanto as camadas internas são as camadas planas. A largura do traço é 7/8 mil, com impedância diferencial de 100 ohms e impedância de terminação única de 56 ohms.

No design de produtos eletrônicos modernos, é bastante comum ter vários barramentos de alimentação em um produto, o que significa que o plano de alimentação em uma placa de quatro camadas será inevitavelmente dividido. Portanto, a presença de cruzamentos de sinal nos splits é inevitável durante o roteamento.

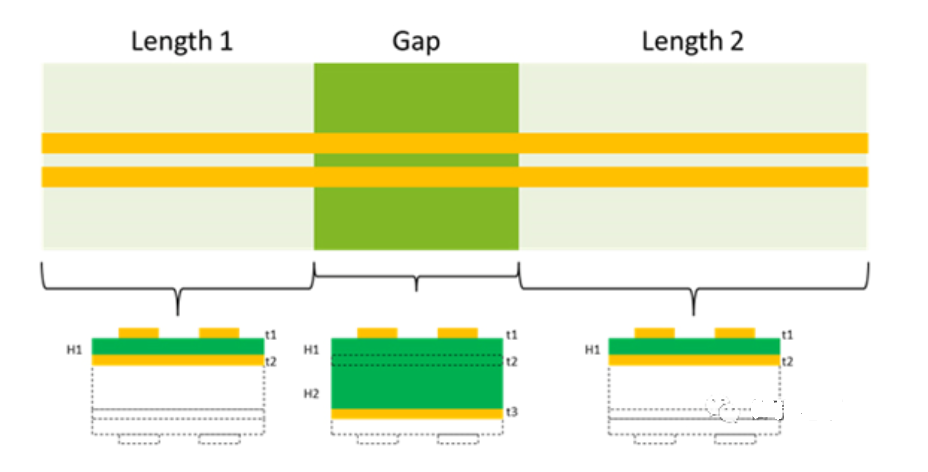

Supondo que um par de linhas de transmissão de superfície cruze uma lacuna de 50 mil de largura entre camadas adjacentes, como mostrado na figura, a seção transversal da linha de microfita antes e depois de passar pela lacuna é ilustrada. A espessura dielétrica H1 da superfície até a camada de referência de potência adjacente é considerada. Como não há planos de referência de potência adjacentes na lacuna, e o próximo plano de referência é o solo adjacente à camada inferior, a espessura dielétrica na lacuna é igual a H1 mais a espessura da camada de potência de 1 onça, mais a próxima camada dielétrica H2. Se a espessura da camada de energia for 1.2mil, então a espessura dielétrica total na lacuna será 51.2mil.

A aproximação de primeira ordem desta topologia é uma combinação de três segmentos de linhas de transmissão com duas impedâncias diferentes. O primeiro e o último segmento têm impedância diferencial de 100 ohm e impedância de terminação única de 56 ohm, enquanto a linha de transmissão na parte do gap tem uma impedância diferencial de 134 ohm e uma impedância de terminação única de 103 ohm. Sua impedância é maior que outras peças, causando reflexão de sinal aqui. A altura e a largura da reflexão são funções do tempo de subida do sinal correspondente e da geometria do intervalo. Quanto mais rápido for o tempo de subida e quanto maior for o intervalo, maior será o reflexo causado. A Figura 3 mostra os resultados da simulação.

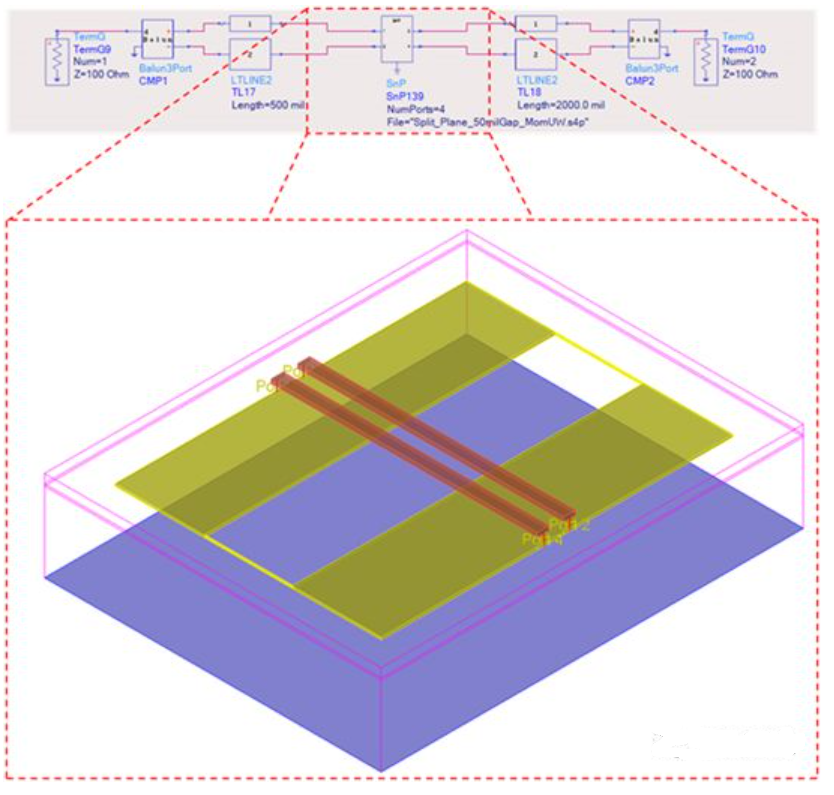

O primeiro e o terceiro segmentos de linhas de transmissão são simulados usando o modelo 2D do TLines-LineType (ADS), enquanto a linha de transmissão no gap é simulada usando um solucionador de campo eletromagnético 3D (Momentum ou EMPro) para obter os efeitos do campo eletromagnético quando o sinal passa. Os materiais dielétricos são os mesmos. Os parâmetros S são extraídos e usados no esquema.

O comprimento total da topologia é de 2.65 polegadas, sendo o comprimento do primeiro segmento da linha de transmissão (L1) de 500 mils e o comprimento do terceiro segmento (L2) de 2 polegadas. A peça 3D é dividida em três segmentos de 50 mils cada para facilitar o ajuste da largura da folga, garantindo ao mesmo tempo que o comprimento total permanece inalterado.

Duas larguras de lacuna são usadas para comparar os efeitos do tamanho da lacuna. Uma lacuna de 50 mil entre os aviões de potência é comum e representa o pior cenário. Uma lacuna de 5 mil é o cenário ideal e também o valor mínimo típico da linha de transmissão até a placa de solda.

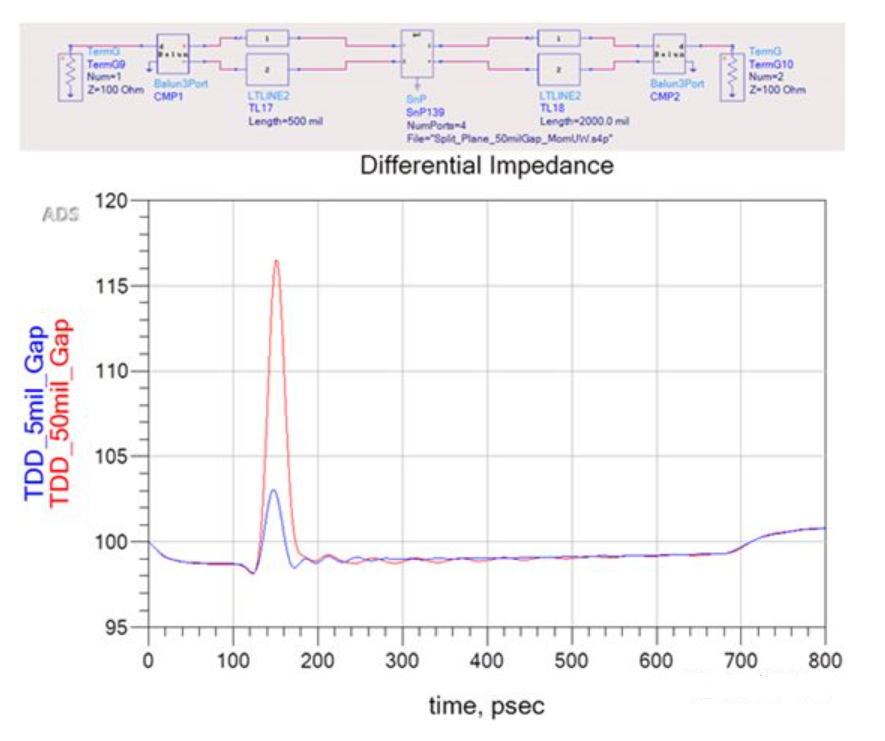

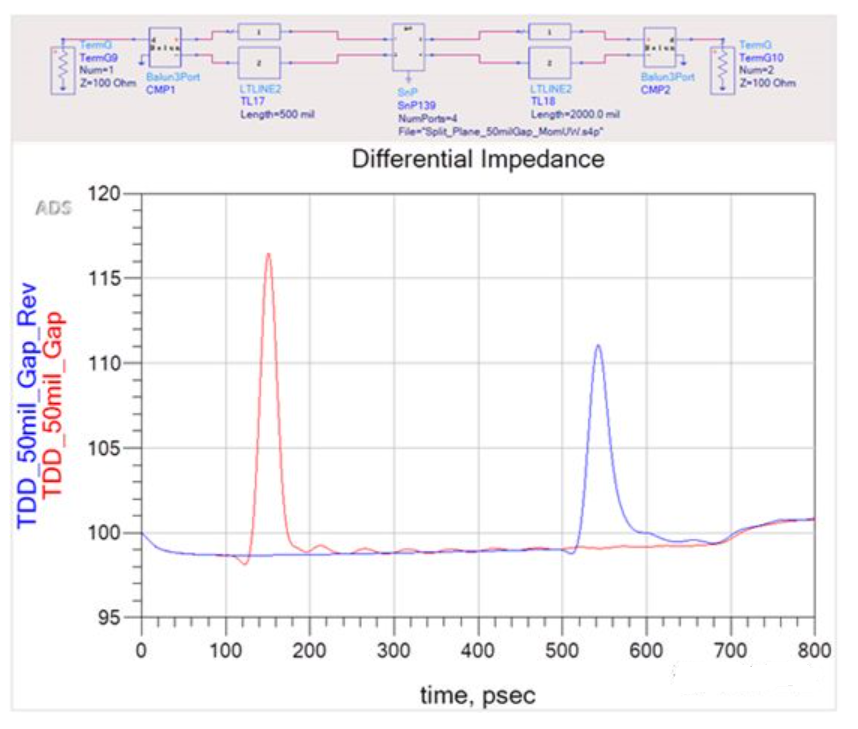

Uma fonte de excitação diferencial é aplicada na porta 1, e a comparação das impedâncias diferenciais é mostrada na Figura 4. Para facilitar a visualização da impedância na porta 2, um conversor balun é usado para converter a porta 4 na porta 2. A curva vermelha representa os resultados para um intervalo de 50 mil, que apresenta maior descontinuidade de impedância em comparação com os resultados para um intervalo de 5 mil (curva azul). Isto ocorre porque a altura do pulso emitido é determinada tanto pelo tempo de subida quanto pela largura do intervalo. Como o tempo de subida é menor em comprimento espacial em comparação com a largura do intervalo, apenas alterar o tempo de subida não pode atingir a descontinuidade máxima da impedância. Isso será demonstrado através da simulação abaixo.

Uma fonte de excitação é aplicada na porta 2, com intervalo de 50 mil, e comparada ao sinal de entrada da porta 1, conforme mostrado na figura a seguir. Devido a um atraso de 2.05 polegadas antes do intervalo, juntamente com perdas na linha de transmissão, a borda do sinal será mais lenta. Como esperado, a amplitude da reflexão é realmente menor.

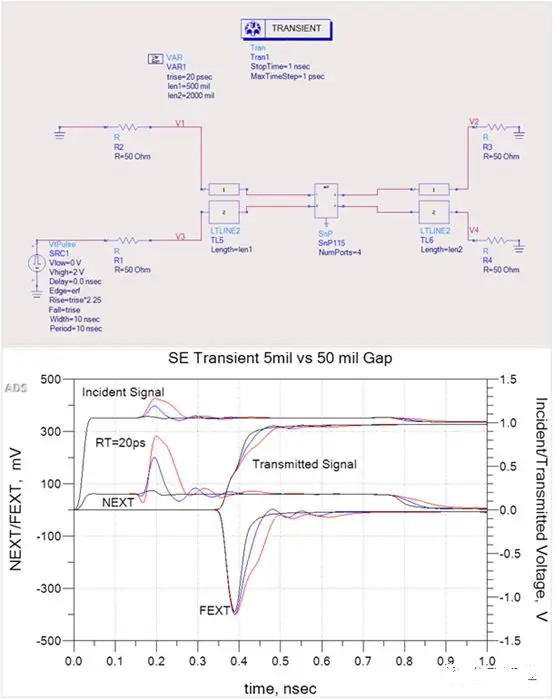

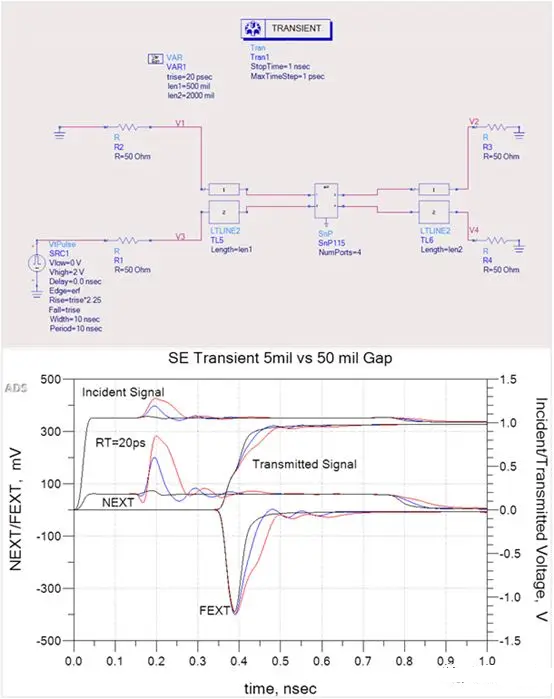

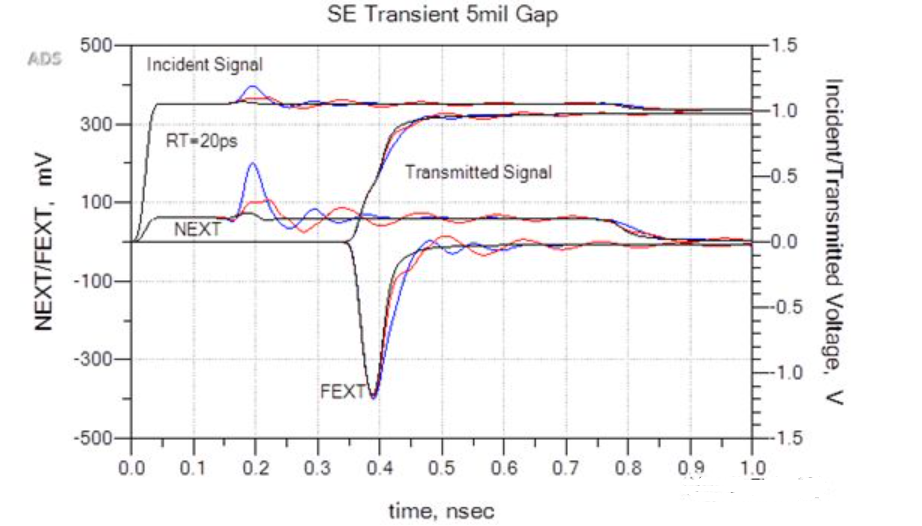

Aqui está a análise do caso single-ended, conforme mostrado na figura. A curva vermelha representa uma lacuna de 50 mil, a curva azul representa uma lacuna de 5 mil e a curva preta representa nenhuma lacuna. Com um tempo de subida de 20 ps, a tensão de reflexão é mais alta quando o intervalo é de 50 mil, resultando em um ligeiro aumento no atraso da linha de transmissão em comparação com o caso sem intervalo.

Em todos os três cenários, variações típicas da curva de diafonia próxima e da extremidade distante podem ser observadas. O forte acoplamento entre as linhas de transmissão através do intervalo resulta em reflexões mais altas, levando a uma maior diafonia próxima.

Aqui está a análise do caso single-ended, conforme mostrado na figura. A curva vermelha representa uma lacuna de 50 mil, a curva azul representa uma lacuna de 5 mil e a curva preta representa nenhuma lacuna. Com um tempo de subida de 20 ps, a tensão de reflexão é mais alta quando o intervalo é de 50 mil, resultando em um ligeiro aumento no atraso da linha de transmissão em comparação com o caso sem intervalo.

Em todos os três cenários, variações típicas da curva de diafonia próxima e da extremidade distante podem ser observadas. Ao passar pela lacuna, o forte acoplamento entre as linhas de transmissão resulta em reflexões mais altas, levando a uma maior diafonia próxima.

Quando há uma lacuna de 50 mil, os pulsos de diafonia próximo aumentam significativamente, enquanto o diafonia distante aumenta apenas ligeiramente. Ao contrário da tensão de diafonia próxima, o valor de pico da tensão de diafonia distante varia com o comprimento do acoplamento. Em um certo atraso de tempo (TD), sua amplitude atinge o pico em cerca de 50% do tempo de subida do sinal da linha de ataque.

Da mesma forma, o sinal da linha de ataque acopla-se à tensão de crosstalk da extremidade oposta, que acopla de volta à linha de ataque, afetando o tempo de subida. A forma de onda na extremidade da linha de ataque é a superposição da tensão de diafonia na extremidade mais distante e a tensão do sinal original, resultando em nenhuma diafonia. Como a extremidade remota está a 2.65 polegadas de distância da extremidade da fonte, a diafonia da extremidade distante está se aproximando da saturação. A redução do comprimento do último segmento da linha de transmissão para 100 mil, conforme mostrado na Figura 7, facilita a compreensão do impacto da lacuna na diafonia da extremidade distante.

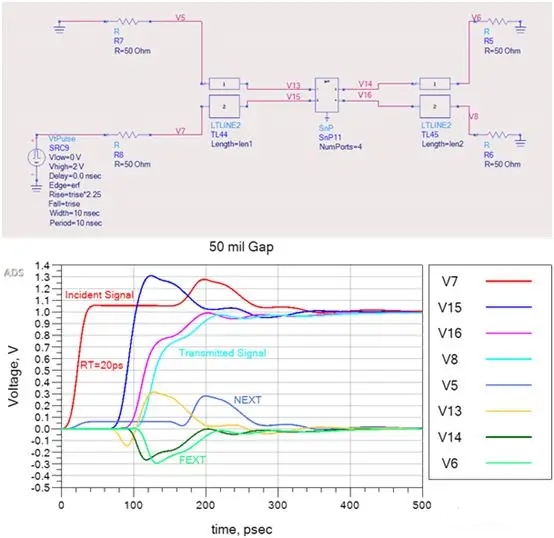

A curva vermelha representa o sinal de entrada (V7) com um tempo de subida de 20 ps, a curva ciano (V8) representa a forma de onda do sinal transmitido na extremidade oposta, azul claro (V5) representa diafonia próxima da extremidade, verde claro ( V6) representa diafonia distante e verde escuro (V15) representa o sinal de ataque no nó V13 após passar pelo TL44. Devido às características de alta impedância na seção de gap, o overshoot causado pelo aumento das reflexões pode ser visto neste segmento da linha de transmissão.

A forma de onda laranja (V13) mostra pulsos de crosstalk negativos na extremidade oposta, consistentes com a borda ascendente do sinal de ataque em V15. Crosstalk próximo também se alinha com a reflexão positiva em V15. À medida que o sinal de ataque sofre um atraso ao passar pelo intervalo, a oscilação de tensão adicional da reflexão aumenta a amplitude dos pulsos de diafonia distante, e sua forma invertida reflete a forma do pulso refletido, como visto na forma de onda verde escura ( V14), que então se acopla de volta ao sinal de ataque e faz com que o tempo de subida diminua até sair da seção de acoplamento, conforme mostrado pela curva magenta (V16).

O problema abordado neste artigo é que quando um sinal passa por um plano segmentado, o sinal transmitido sofre reflexões positivas e negativas devido a incompatibilidades de impedância, sendo o tempo de reflexão igual ao tempo que leva para passar pelo gap. Isto aumenta a amplitude do sinal e dos pulsos de diafonia na extremidade distante, diminuindo assim o tempo de subida do sinal transmitido em proporção à forma de onda da diafonia na extremidade distante.

Levando em consideração múltiplos caminhos de retorno no plano segmentado e nas bordas, uma antena de slot eficaz é formada, irradiando ruído para fora. Para atender aos requisitos de radiação EMI FCC Classe B (campo de 3 metros), o ruído irradiado deve ser inferior a 100 mV/m entre 30-80 MHz e inferior a 200 mV/m entre 216 MHz-1 GHz.

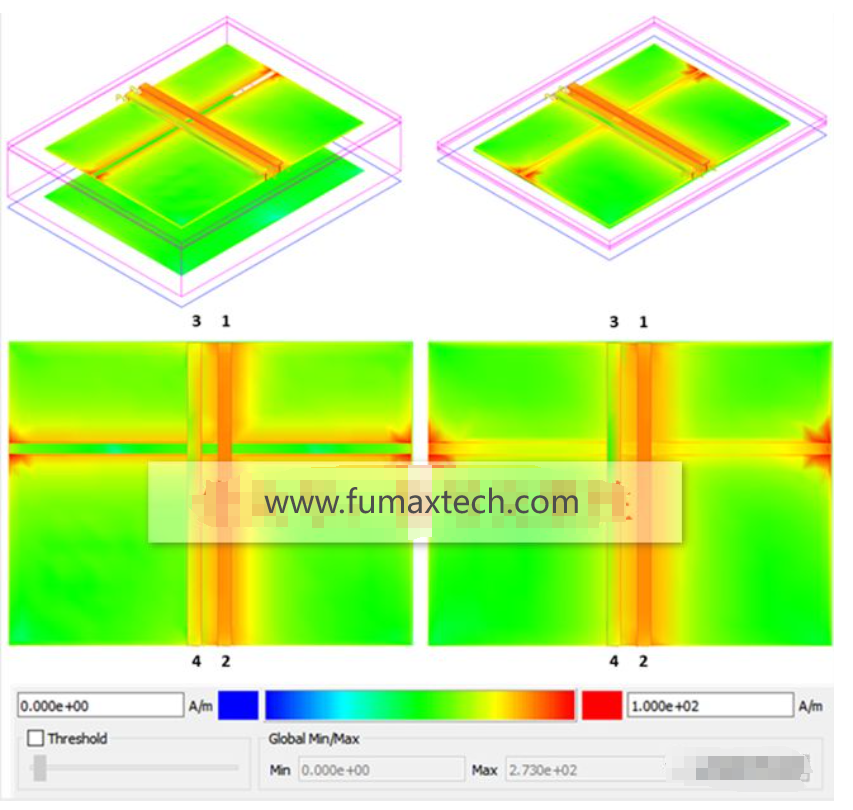

Quando as linhas de microfita passam através de planos segmentados, o ruído pode irradiar para o espaço livre devido a caminhos de retorno descontínuos e à falta de blindagem. A visualização da densidade da corrente de retorno no intervalo entre planos de referência adjacentes pode ser obtida através de software de simulação 3D.

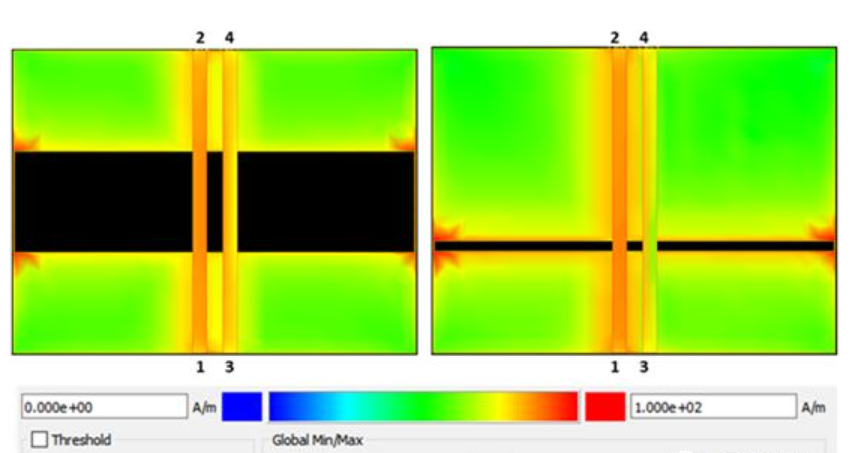

A Figura 8 compara a densidade de corrente de retorno de sinal de terminação única em planos de referência adjacentes. À esquerda, uma onda senoidal de 4 GHz passa por um intervalo de 50 mil, enquanto à direita passa por um intervalo de 5 mil. A escolha de um sinal de 4 GHz se deve ao fato de ele representar a frequência Nyquist de 8 Gbps PCIe Gen 3 em uma placa PCIe típica de 4 camadas. Ao conduzir o sinal da porta 1 para a porta 2 com as portas 3 e 4 devidamente terminadas, a distribuição da densidade da corrente de retorno no plano de referência na segmentação pode ser claramente observada.

Observe o ligeiro aumento na densidade de corrente nas bordas da lacuna onde a linha da vítima está localizada. Isto indica que a corrente de retorno nas linhas adjacentes causa tensão adicional de diafonia na extremidade distante, conforme discutido anteriormente. Desta perspectiva, linhas de terminação única que cruzam a segmentação podem não ser uma abordagem ideal.

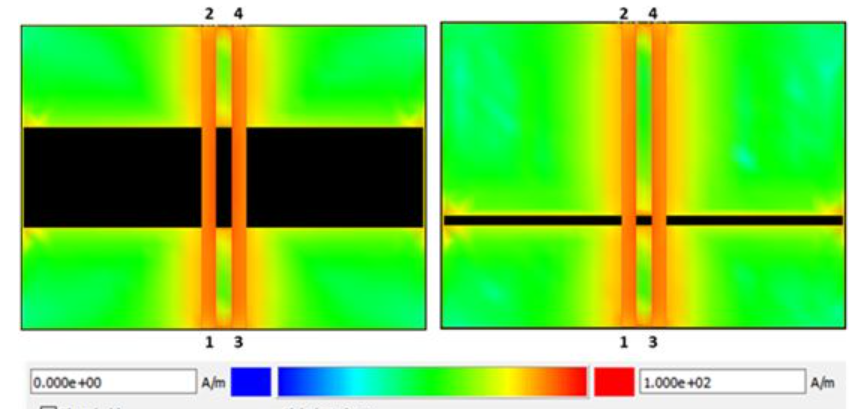

A Figura 9 mostra a densidade da corrente de retorno no plano de referência quando um sinal diferencial de 4 GHz passa por intervalos de 50 mil (esquerda) e 5 mil (direita). Pode-se observar que a densidade máxima de corrente entre os dois pares diferenciais está concentrada nas bordas da segmentação, com apenas uma pequena porção se propagando ao longo do gap.

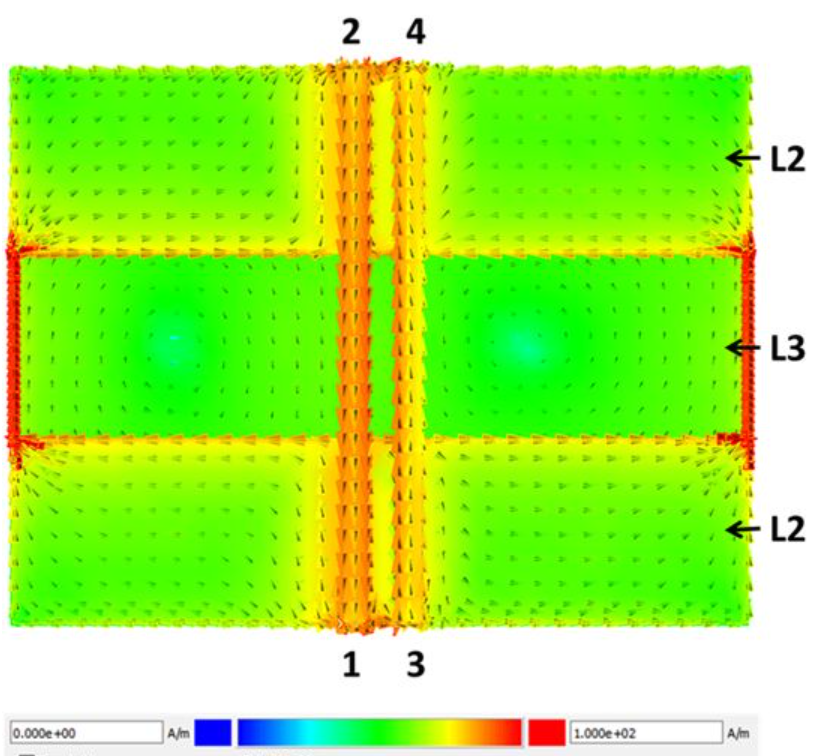

Quando um sinal de terminação única é recebido da porta 1 para a porta 2, com as outras portas terminadas, a Figura 10 exibe a direção das correntes nas camadas planas L2 e L3. Pode-se observar que quando a direção da corrente é da porta 2 para a porta 1, a corrente de retorno em L2 é dividida em duas partes na extremidade do intervalo (lado da porta 1). Além disso, existem duas correntes de rotação reversa em L3, concentradas principalmente nas metades esquerda e direita do gap. Estas são causadas por correntes de rotação reversa ao longo da borda da lacuna em L2, injetando energia EM na cavidade plana. Vale ressaltar que o sentido das correntes rotativas em L2 e L3 é oposto.

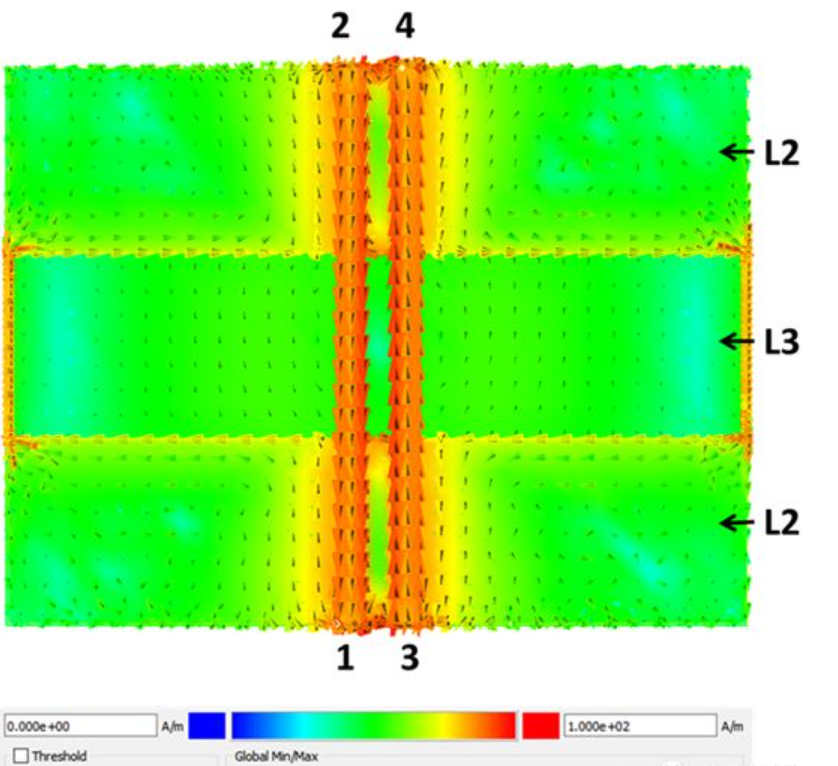

Porém, quando um sinal diferencial é aplicado às duas linhas de transmissão, conforme mostrado na Figura 11, pode-se observar que o sentido da corrente ao longo da borda do gap é o mesmo. É importante notar também que a corrente rotativa em L3 é unidirecional, concentrada entre os pares diferenciais e o gap. A questão aqui é que mesmo quando um sinal diferencial é aplicado às duas linhas de transmissão, ainda há corrente fluindo para a borda da lacuna, introduzindo ruído na cavidade plana e irradiando para o espaço livre, causando EMI.

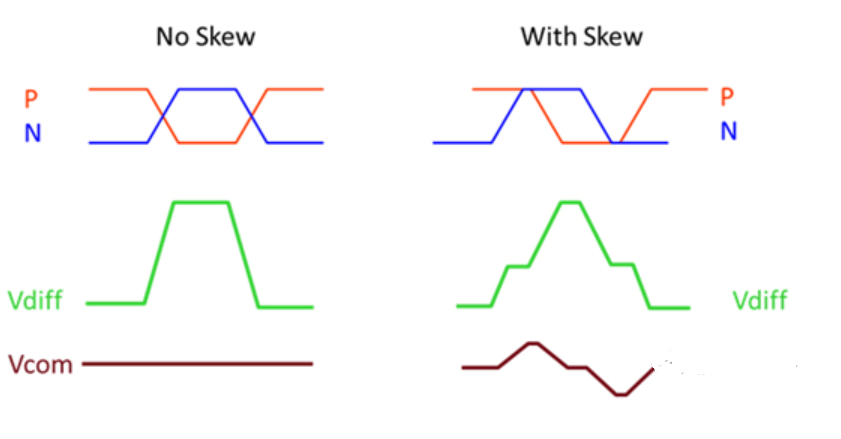

Na análise anterior, o exemplo de um par diferencial assumiu um emparelhamento interno perfeito, mas na realidade tais casos são raros. Fatores como comprimentos de roteamento desiguais, efeitos de fibra de vidro, diferenças nos comprimentos dos pinos do conector ou assimetria nas vias diferenciais ao alterar as camadas podem levar a incompatibilidades de atraso interno. Quando estas situações ocorrem, alguns sinais de modo comum podem ser convertidos em sinais de modo diferencial. Conforme mostrado na Figura 12, o grau de conversão depende da incompatibilidade de atraso interno. Num par diferencial ideal, Vdiff representa a diferença de tensão entre os sinais P e N. Se a diferença de fase for de 180 graus, a tensão de modo comum dobrará e não haverá tensão de modo comum. Contudo, quando há uma inclinação, a diferença de fase do par diferencial não é de 180 graus. Considerando a inclinação, o sinal diferencial será deformado, resultando em uma tensão de modo comum (Vcom). A magnitude e a forma da tensão de modo comum são proporcionais ao deslocamento de fase. Se as fases de P e N forem idênticas, não há tensão diferencial e tudo se torna tensão de modo comum. A tensão de modo comum também requer um caminho de retorno e, se o caminho for interrompido, sua corrente de retorno passará pelo plano dividido de forma semelhante às correntes de retorno de terminação única.

De acordo com algumas especificações de fiação PCIe, a distorção do pior caso é 0.21UI (uma UI representa o tempo de um bit). No PCIe Gen3 8 Gbps, um deslocamento de 0.21UI corresponde a 26.3ps. O cenário passando por um intervalo de 50mil equivale a uma mudança de fase interna, conforme mostrado na Figura 13, comparado com a situação ideal. Como esperado, a tensão de modo comum passa através do plano de partição, e a corrente de retorno de modo comum é semelhante à situação com linhas de terminação única que passam pelo plano de partição (Figura 8). A única diferença é que não há 100% de corrente de modo comum, portanto também haverá corrente de retorno de modo diferencial.

A questão final a ser abordada é que se houver uma camada dielétrica extremamente fina entre a camada de solo adjacente e a camada de energia particionada, ela servirá como um melhor caminho de retorno ao passar pela camada particionada. Logicamente, isto faz sentido do ponto de vista da integridade do sinal, uma vez que a impedância das linhas de transmissão diminui com o aumento da espessura dielétrica entre a linha de transmissão e o plano de referência particionado.

Nos exemplos anteriores, assumimos uma placa de quatro camadas com espessura de 62 mils. Isto quase determina a espessura do dielétrico da camada interna na pilha. Para mover o plano de referência para mais perto da lacuna entre os planos de potência, a contagem de camadas do PCB precisa ser aumentada para pelo menos 6 camadas para manter a simetria da pilha e a espessura total.

Se a espessura do dielétrico abaixo da folga for reduzida, simulando novamente a folga de 5 mils, caso de extremidade única, os resultados são mostrados na Figura 14. Esta fina camada dielétrica é ajustada para 2 mils, que é uma espessura comum para desacoplamento núcleos de capacitância enterrados no plano de potência. Adicionando a espessura de 5 mils para H1 e 1.2 mils para o plano de potência L2, conforme mostrado na Figura 1, a espessura dielétrica total abaixo da folga é de 8.2 mils.

Na imagem à esquerda, a maior parte da corrente de retorno é desviada em torno da lacuna no plano de referência L2. Na imagem da direita, quando o sinal passa pelo intervalo, a maior parte da corrente de retorno flui em direção ao plano de referência L3 abaixo da linha de transmissão, mas alguma corrente ainda permanece perto do intervalo em L2, irradiando assim algum ruído.

Do ponto de vista da integridade do sinal, os sinais refletidos e o ruído de diafonia próximo foram essencialmente reduzidos pela metade, conforme mostrado na Figura 15. Há menos atenuação no tempo de subida do sinal transmitido, e o diafonia distante também foi melhorado .

Voltando à questão principal, qual perspectiva está correta? Nenhum dos dois está totalmente correto. Este artigo discute vários cenários de linhas de microfita passando por planos divididos. Do ponto de vista da integridade do sinal, sob certas condições, pode ser aceitável que linhas de microfita passem através de planos divididos. Por exemplo, na simulação acima, desde que a lacuna entre os planos divididos seja reduzida para 5mil e uma fina camada dielétrica seja adicionada entre as camadas planas adjacentes, a diafonia não aumenta significativamente. De acordo com as tolerâncias reais de ruído, isto pode não ter impacto.

No entanto, do ponto de vista da EMC, ainda existem mais riscos e preocupações. Nunca existe um cenário em que alguma corrente de retorno nunca flua para a borda da lacuna do plano dividido, portanto ainda existe o risco de EMI. Devido à multiplicidade de fatores inter-relacionados nos projetos reais, é um desafio ter uma regra universal aplicável aqui ou em qualquer outra situação.

Geralmente, as linhas de microfita devem evitar cruzar planos divididos. No entanto, quando a análise detalhada do layout real e do empilhamento das placas não for viável, métodos alternativos para mitigar a radiação de ruído, como a adição de blindagem externa adicional, podem ser explorados.

Em última análise, este artigo enfatiza que em projetos modernos de alta velocidade, não podemos nos limitar a considerar apenas a integridade do sinal, a integridade da potência ou a EMC individualmente. Todos os três devem ser considerados simultaneamente. Se considerarmos apenas a integridade do sinal sem considerações de EMC, poderemos tirar conclusões incorretas, levando a possíveis falhas nos testes de compatibilidade de EMC do produto final.