Nota del editor: en los diseños modernos de alta velocidad, no es suficiente analizar la integridad de la señal, la integridad de la energía y la EMC por separado; un enfoque holístico es esencial para un diseño exitoso.

Problema de fondo: cuando las señales cruzan áreas de segmentación entre planos de referencia adyacentes en una capa, a menudo surgen discusiones sobre la integridad de la señal. Algunos argumentan que las señales no deberían cruzar la segmentación, ya que puede aumentar la diafonía y los problemas de EMC, mientras que otros sugieren que con un diseño cuidadoso de la acumulación de capas y el ancho de los espacios de segmentación en los planos de alimentación/tierra, no debería haber ningún problema. Entonces, ¿cuál es el enfoque correcto? Por supuesto, la mejor respuesta es "¡depende!" Este artículo explora el escenario en el que las señales pasan a través de planos segmentados.

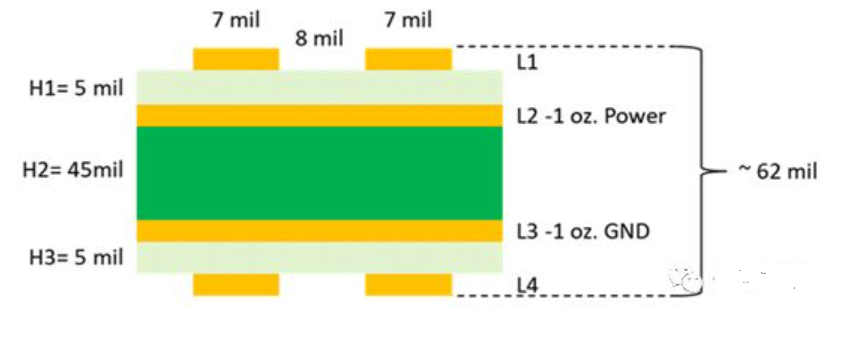

Primero, consideremos un típico PCB de cuatro capas apilamiento con un espesor total de 62 mils. La capa superficial es la capa de señal, mientras que las capas internas son las capas planas. El ancho de la traza es de 7/8 mil, con una impedancia diferencial de 100 ohmios y una impedancia de un solo extremo de 56 ohmios.

En el diseño de productos electrónicos modernos, es bastante común tener múltiples rieles de alimentación en un producto, lo que significa que el plano de alimentación en una placa de cuatro capas inevitablemente estará dividido. Por lo tanto, la presencia de cruces de señales sobre divisiones es inevitable durante el enrutamiento.

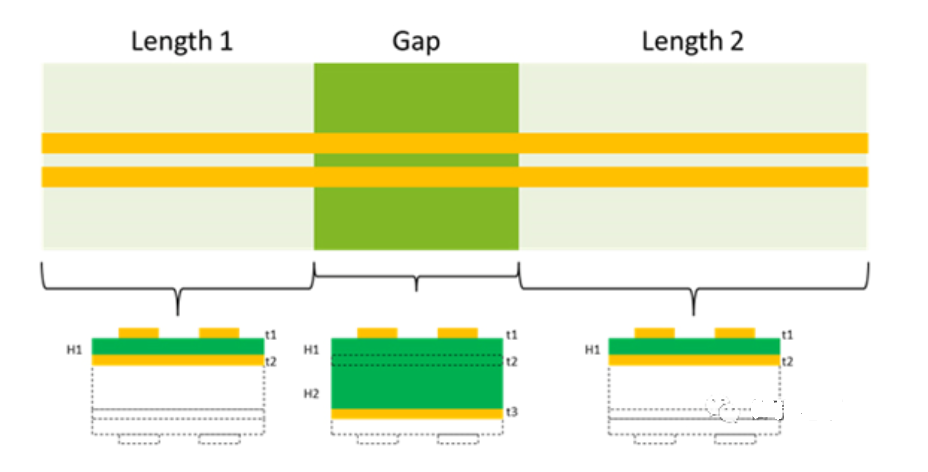

Suponiendo que un par de líneas de transmisión superficial cruzan un espacio de 50 mil de ancho entre capas adyacentes, como se muestra en la figura, se ilustra la sección transversal de la línea de microcinta antes y después de pasar a través del espacio. Se considera el espesor dieléctrico H1 desde la superficie hasta la capa de referencia de potencia adyacente. Dado que no hay planos de referencia de energía adyacentes en el espacio, y el siguiente plano de referencia es el suelo adyacente a la capa inferior, el espesor dieléctrico en el espacio es igual a H1 más el espesor de la capa de energía de 1 oz, más la siguiente capa dieléctrica. H2. Si el espesor de la capa de energía es de 1.2 mil, entonces el espesor dieléctrico total en el espacio es de 51.2 mil.

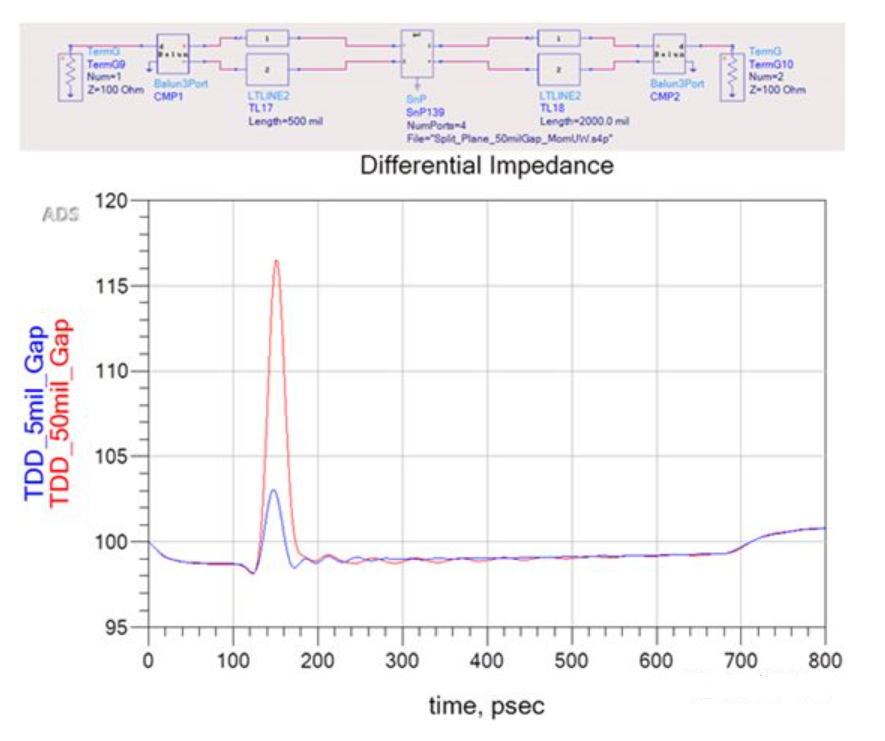

La aproximación de primer orden de esta topología es una combinación de tres segmentos de líneas de transmisión con dos impedancias diferentes. El primer y último segmento tienen una impedancia diferencial de 100 ohmios y una impedancia de un solo extremo de 56 ohmios, mientras que la línea de transmisión en la parte de separación tiene una impedancia diferencial de 134 ohmios y una impedancia de un solo extremo de 103 ohmios. Su impedancia es mayor que la de otras partes, lo que provoca que la señal se refleje aquí. La altura y el ancho de la reflexión son funciones del tiempo de subida de la señal correspondiente y de la geometría del espacio. Cuanto más rápido sea el tiempo de subida y cuanto más amplia sea la brecha, mayor será la reflexión provocada. La Figura 3 muestra los resultados de la simulación.

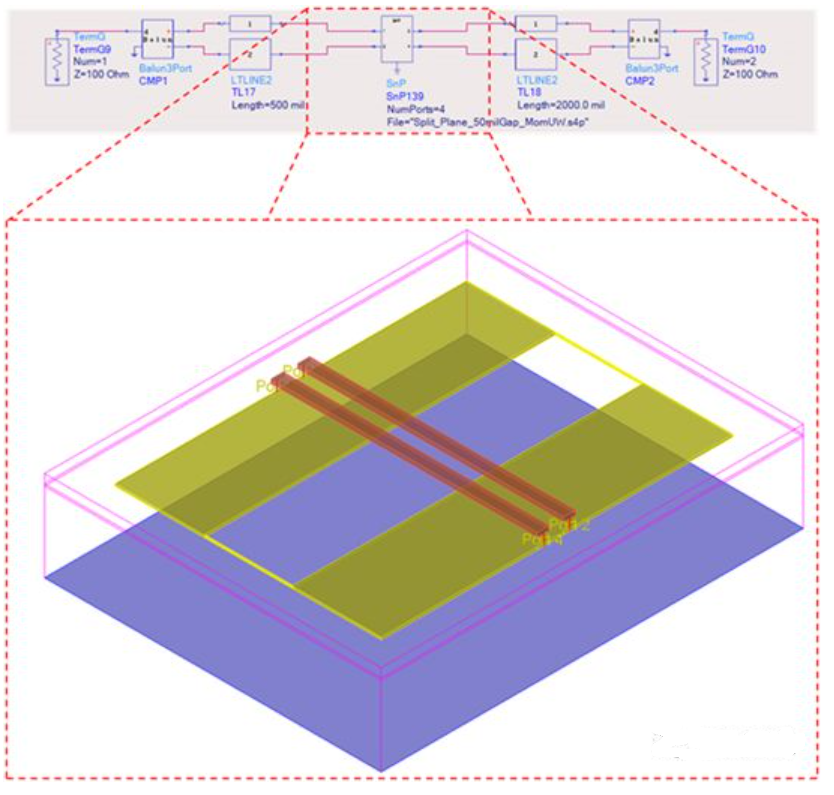

El primer y tercer segmento de líneas de transmisión se simulan usando el modelo 2D de TLines-LineType (ADS), mientras que la línea de transmisión en el espacio se simula usando un solucionador de campos electromagnéticos 3D (Momentum o EMPro) para obtener los efectos del campo electromagnético cuando el la señal pasa. Los materiales dieléctricos son los mismos. Los parámetros S se extraen y utilizan en el esquema.

La longitud total de la topología es de 2.65 pulgadas, siendo la longitud del primer segmento de la línea de transmisión (L1) de 500 mils y la longitud del tercer segmento (L2) de 2 pulgadas. La pieza 3D está dividida en tres segmentos de 50 mils cada uno para facilitar el ajuste del ancho del espacio y al mismo tiempo garantizar que la longitud total permanezca sin cambios.

Se utilizan dos anchos de espacio para comparar los efectos del tamaño del espacio. Una brecha de 50 mil entre aviones propulsores es común y representa el peor de los casos. Un espacio de 5 mil es el escenario óptimo y también es el valor mínimo típico desde la línea de transmisión hasta la plataforma de soldadura.

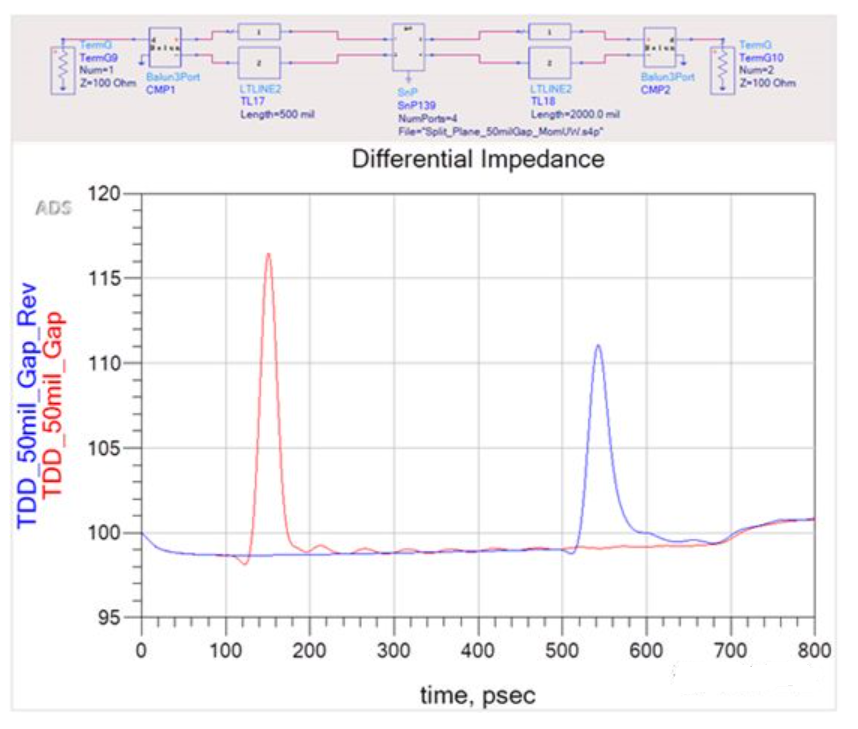

Se aplica una fuente de excitación diferencial en el puerto 1 y la comparación de impedancias diferenciales se muestra en la Figura 4. Para facilitar la visualización de la impedancia en el puerto 2, se utiliza un convertidor balun para convertir el puerto 4 en el puerto 2. La curva roja representa los resultados. para una separación de 50 mil, que muestra una mayor discontinuidad de impedancia en comparación con los resultados para una separación de 5 mil (curva azul). Esto se debe a que la altura del pulso emitido está determinada tanto por el tiempo de subida como por el ancho del espacio. Dado que el tiempo de subida es menor en longitud espacial en comparación con el ancho del espacio, cambiar únicamente el tiempo de subida no puede lograr la discontinuidad de impedancia máxima. Esto se demostrará mediante la simulación a continuación.

Se aplica una fuente de excitación en el puerto 2, con una separación de 50 mil, y se compara con la señal de entrada del puerto 1, como se muestra en la siguiente figura. Debido a un retraso de 2.05 pulgadas antes del espacio, junto con pérdidas en la línea de transmisión, el borde de la señal será más lento. Como era de esperar, la amplitud de la reflexión es efectivamente menor.

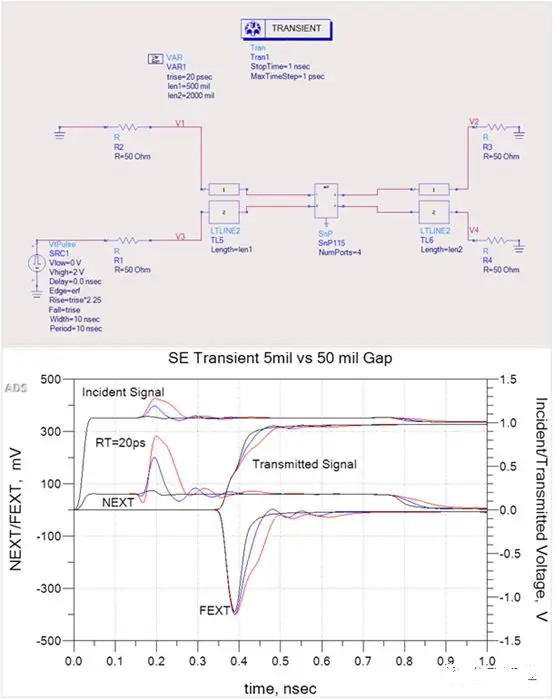

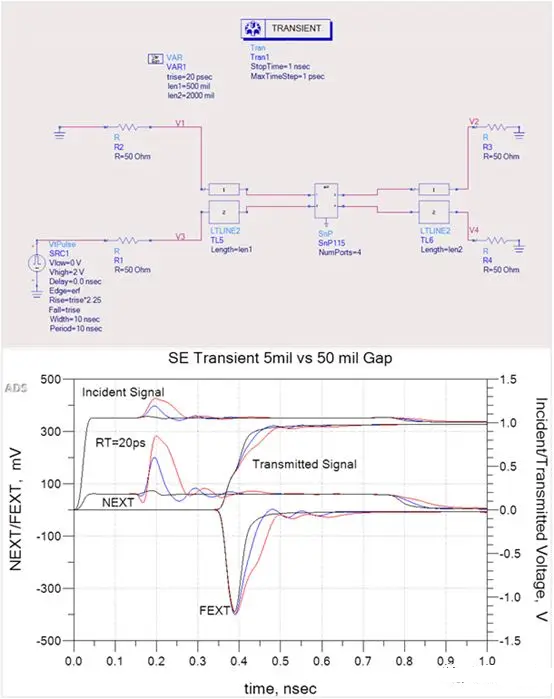

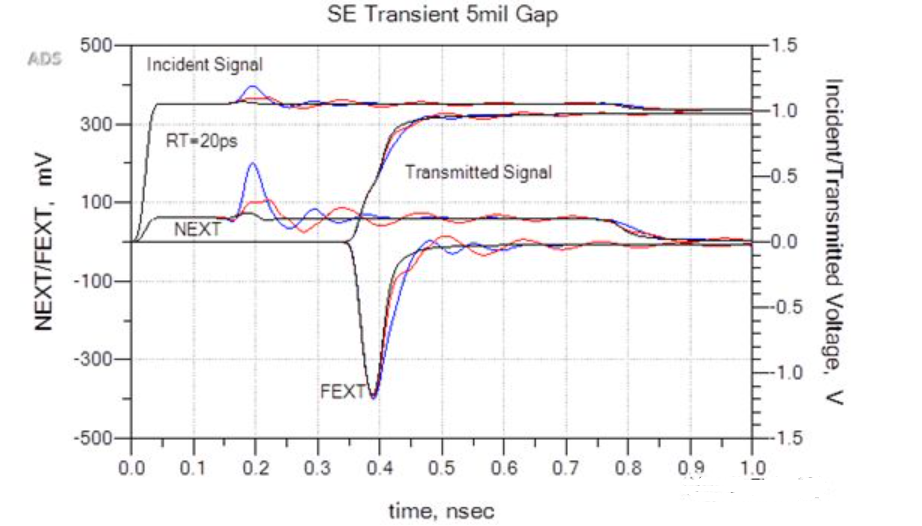

Aquí está el análisis del caso de un solo extremo, como se muestra en la figura. La curva roja representa una brecha de 50 mil, la curva azul representa una brecha de 5 mil y la curva negra representa ninguna brecha. Con un tiempo de subida de 20 ps, el voltaje de reflexión es más alto cuando la separación es de 50 mil, lo que da como resultado un ligero aumento en el retardo de la línea de transmisión en comparación con el caso sin separación.

En los tres escenarios, se pueden observar variaciones típicas de la curva de diafonía en el extremo cercano y en el extremo lejano. El estrecho acoplamiento entre las líneas de transmisión a través del espacio produce reflexiones más altas, lo que genera una mayor diafonía en el extremo cercano.

Aquí está el análisis del caso de un solo extremo, como se muestra en la figura. La curva roja representa una brecha de 50 mil, la curva azul representa una brecha de 5 mil y la curva negra representa ninguna brecha. Con un tiempo de subida de 20 ps, el voltaje de reflexión es más alto cuando la separación es de 50 mil, lo que da como resultado un ligero aumento en el retardo de la línea de transmisión en comparación con el caso sin separación.

En los tres escenarios, se pueden observar variaciones típicas de la curva de diafonía en el extremo cercano y en el extremo lejano. Al pasar a través del espacio, el estrecho acoplamiento entre las líneas de transmisión da como resultado reflexiones más altas, lo que genera una mayor diafonía en el extremo cercano.

Cuando hay una brecha de 50 mil, los pulsos de diafonía en el extremo cercano aumentan significativamente, mientras que la diafonía en el extremo lejano solo aumenta ligeramente. A diferencia del voltaje de diafonía del extremo cercano, el valor máximo del voltaje de diafonía del extremo lejano varía con la longitud del acoplamiento. En un cierto retardo de tiempo (TD), su amplitud alcanza un máximo alrededor del 50% del tiempo de subida de la señal de la línea atacante.

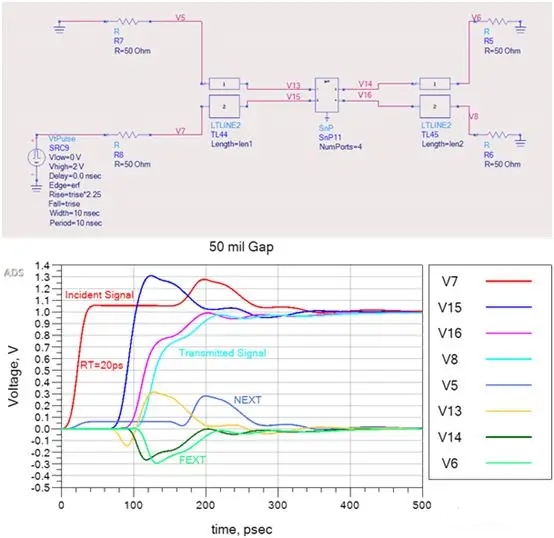

De manera similar, la señal de la línea atacante se acopla al voltaje de diafonía del extremo lejano, que se vuelve a acoplar a la línea atacante, lo que afecta el tiempo de subida. La forma de onda en el extremo lejano de la línea de ataque es la superposición del voltaje de diafonía del extremo lejano y el voltaje de la señal original, lo que no produce diafonía. Como el extremo lejano está a 2.65 pulgadas del extremo fuente, la diafonía del extremo lejano se acerca a la saturación. Reducir la longitud del último segmento de la línea de transmisión a 100 mil, como se muestra en la Figura 7, hace que sea más fácil comprender el impacto de la brecha en la diafonía del extremo lejano.

La curva roja representa la señal de entrada (V7) con un tiempo de subida de 20 ps, la curva cian (V8) representa la forma de onda de la señal transmitida en el extremo lejano, el azul claro (V5) representa la diafonía del extremo cercano, el verde claro ( V6) representa la diafonía en el extremo lejano y el verde oscuro (V15) representa la señal de ataque en el nodo V13 después de pasar por TL44. Debido a las características de alta impedancia en la sección de separación, se puede observar un exceso causado por un aumento de reflexiones en este segmento de línea de transmisión.

La forma de onda naranja (V13) muestra pulsos de diafonía negativos en el extremo lejano, consistentes con el flanco ascendente de la señal de ataque en V15. La diafonía del extremo cercano también se alinea con la reflexión positiva en V15. A medida que la señal atacante experimenta un retraso al pasar a través del espacio, la oscilación de voltaje adicional de la reflexión aumenta la amplitud de los pulsos de diafonía del extremo lejano y su forma invertida refleja la forma del pulso reflejado, como se ve en la forma de onda verde oscuro ( V14), que luego se vuelve a acoplar a la señal de ataque y hace que el tiempo de subida decaiga hasta abandonar la sección de acoplamiento, como se muestra en la curva magenta (V16).

El problema abordado en este artículo es que cuando una señal pasa a través de un plano segmentado, la señal transmitida sufre reflexiones positivas y negativas debido a desajustes de impedancia, siendo el tiempo de reflexión igual al tiempo que tarda en atravesar el espacio. Esto aumenta la amplitud de la señal y los pulsos de diafonía del extremo lejano, ralentizando así el tiempo de subida de la señal transmitida en proporción a la forma de onda de la diafonía del extremo lejano.

Teniendo en cuenta múltiples caminos de retorno en el plano segmentado y los bordes, se forma una antena de ranura efectiva que irradia ruido hacia afuera. Para cumplir con los requisitos de radiación EMI FCC Clase B (campo de 3 metros), el ruido radiado debe ser inferior a 100 mV/m entre 30 y 80 MHz y menos de 200 mV/m entre 216 MHz y 1 GHz.

Cuando las líneas microstrip pasan a través de planos segmentados, el ruido puede irradiarse al espacio libre debido a caminos de retorno discontinuos y falta de blindaje. La visualización de la densidad de corriente de retorno en el espacio entre planos de referencia adyacentes se puede lograr mediante un software de simulación 3D.

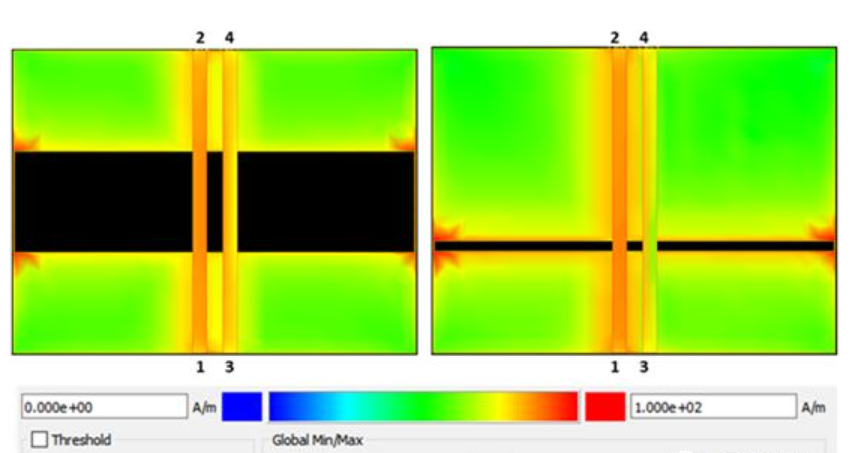

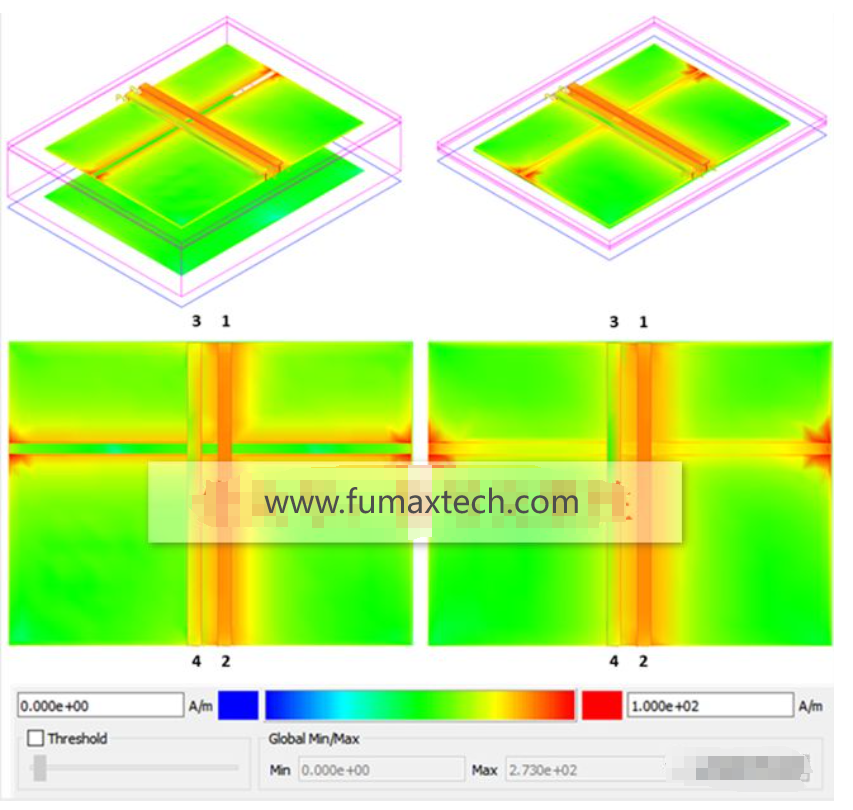

La Figura 8 compara la densidad de corriente de retorno de la señal de un solo extremo en planos de referencia adyacentes. A la izquierda, una onda sinusoidal de 4 GHz pasa a través de un espacio de 50 mil, mientras que a la derecha pasa a través de un espacio de 5 mil. La elección de una señal de 4 GHz se debe a que representa la frecuencia Nyquist de PCIe Gen 8 de 3 Gbps en una placa PCIe típica de 4 capas. Al conducir la señal desde el puerto 1 al puerto 2 con los puertos 3 y 4 correctamente terminados, se puede observar claramente la distribución de la densidad de corriente de retorno en el plano de referencia en la segmentación.

Observe el ligero aumento en la densidad de corriente en los bordes del espacio donde se encuentra la línea de la víctima. Esto indica que la corriente de retorno en líneas adyacentes provoca un voltaje de diafonía adicional en el extremo lejano, como se analizó anteriormente. Desde esta perspectiva, las líneas de un solo extremo que cruzan la segmentación pueden no ser un enfoque óptimo.

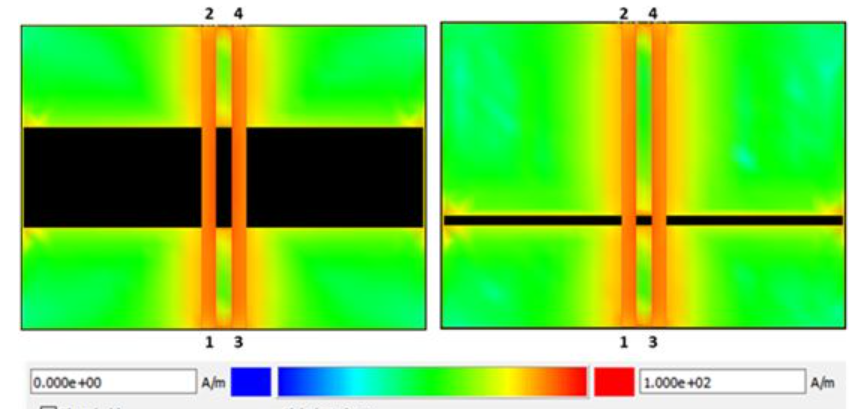

La Figura 9 muestra la densidad de corriente de retorno en el plano de referencia cuando una señal diferencial de 4 GHz pasa a través de espacios de 50 mil (izquierda) y 5 mil (derecha). Se puede observar que la densidad de corriente máxima entre los dos pares diferenciales se concentra en los bordes de la segmentación, y solo una pequeña porción se propaga a lo largo del espacio.

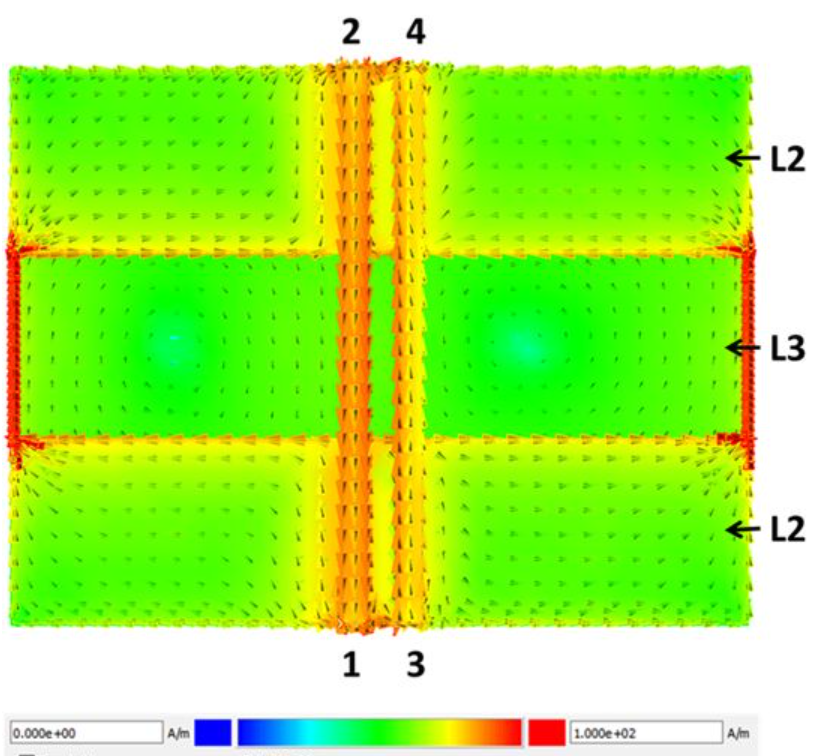

Cuando se introduce una señal de un solo extremo desde el puerto 1 al puerto 2, con los otros puertos terminados, la Figura 10 muestra la dirección de las corrientes en las capas planas L2 y L3. Se puede observar que cuando la dirección actual es del puerto 2 al puerto 1, la corriente de retorno en L2 se divide en dos partes en el extremo más alejado del espacio (lado del puerto 1). Además, hay dos corrientes de rotación inversa en L3, concentradas principalmente en las mitades izquierda y derecha del espacio. Estos son causados por corrientes de rotación inversa a lo largo del borde del espacio en L2 que inyectan energía EM en la cavidad plana. Es de destacar que la dirección de las corrientes giratorias en L2 y L3 es opuesta.

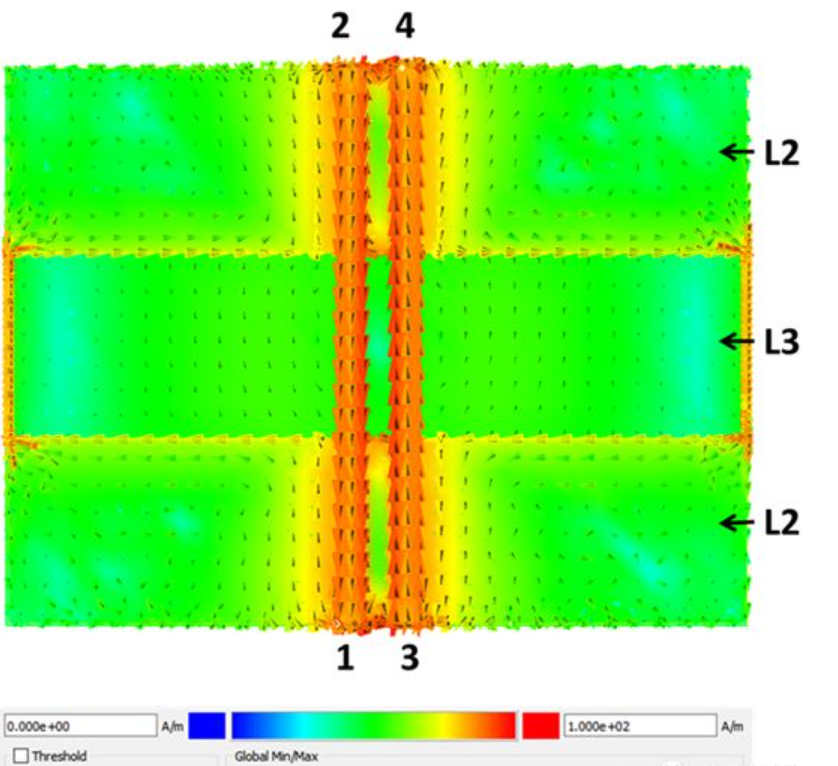

Sin embargo, cuando se aplica una señal diferencial a las dos líneas de transmisión, como se muestra en la Figura 11, se puede observar que la dirección de la corriente a lo largo del borde del espacio es la misma. También es importante señalar que la corriente giratoria en L3 es unidireccional y se concentra entre los pares diferenciales y el espacio. El problema aquí es que incluso cuando se aplica una señal diferencial a las dos líneas de transmisión, todavía fluye corriente hacia el borde del espacio, lo que introduce ruido en la cavidad plana y se irradia al espacio libre, lo que provoca EMI.

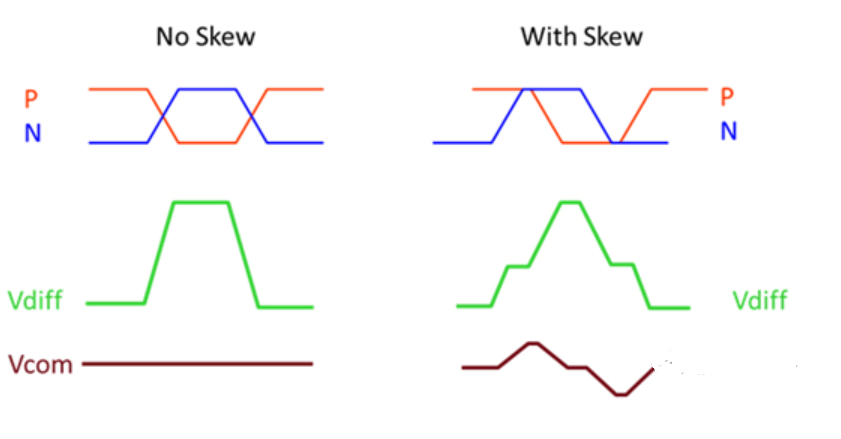

En el análisis anterior, el ejemplo de un par diferencial suponía una coincidencia interna perfecta, pero en realidad, estos casos son raros. Factores como longitudes de enrutamiento desiguales, efectos de fibra de vidrio, diferencias en las longitudes de los pines del conector o asimetría en las vías diferenciales al cambiar de capa pueden provocar discrepancias en los retardos internos. Cuando ocurren estas situaciones, algunas señales de modo común se pueden convertir en señales de modo diferencial. Como se muestra en la Figura 12, el grado de conversión depende del desajuste del retardo interno. En un par diferencial ideal, Vdiff representa la diferencia de voltaje entre las señales P y N. Si su diferencia de fase es de 180 grados, el voltaje de modo común se duplicará y no habrá voltaje de modo común. Sin embargo, cuando hay un sesgo, la diferencia de fase del par diferencial no es de 180 grados. Teniendo en cuenta la inclinación, la señal diferencial se deformará, lo que dará como resultado un voltaje de modo común (Vcom). La magnitud y forma del voltaje de modo común son proporcionales al desfase. Si las fases de P y N son idénticas, no hay voltaje diferencial y todo se convierte en voltaje de modo común. El voltaje de modo común también requiere una ruta de retorno, y si la ruta se interrumpe, su corriente de retorno pasará a través del plano dividido de manera similar a las corrientes de retorno de un solo extremo.

Según algunas especificaciones de cableado PCIe, la desviación en el peor de los casos es 0.21 UI (una UI representa el tiempo de un bit). En PCIe Gen3 de 8 Gbps, un desplazamiento de 0.21 UI corresponde a 26.3 ps. El escenario que atraviesa una brecha de 50 mil equivale a un cambio de fase interno, como se muestra en la Figura 13, en comparación con la situación ideal. Como se esperaba, el voltaje de modo común pasa a través del plano de partición y la corriente de retorno de modo común es similar a la situación con líneas de un solo extremo que pasan a través del plano de partición (Figura 8). La única diferencia es que no hay una corriente de modo común al 100%, por lo que también habrá una corriente de retorno en modo diferencial.

El último problema a abordar es que si hay una capa dieléctrica extremadamente delgada entre la capa de tierra adyacente y la capa de energía dividida, servirá como una mejor ruta de retorno al pasar a través de la capa dividida. Lógicamente, esto tiene sentido desde la perspectiva de la integridad de la señal, ya que la impedancia de las líneas de transmisión disminuye con el aumento del espesor dieléctrico entre la línea de transmisión y el plano de referencia dividido.

En los ejemplos anteriores, asumimos un tablero de cuatro capas con un espesor de 62 mils. Esto casi determina el espesor de la capa dieléctrica interna de la pila. Para acercar el plano de referencia al espacio entre los planos de potencia, es necesario aumentar el número de capas de PCB a al menos 6 capas para mantener la simetría de la pila y el espesor total.

Si se reduce el espesor del dieléctrico debajo del espacio, volviendo a simular el espacio de 5 mil, caso de un solo extremo, los resultados se muestran en la Figura 14. Esta delgada capa dieléctrica se establece en 2 mil, que es un espesor común para desacoplamiento. Núcleos de capacitancia enterrados en el plano de potencia. Sumando el espesor de 5 mils para H1 y 1.2 mils para el plano de potencia L2, como se muestra en la Figura 1, el espesor dieléctrico total debajo del espacio es de 8.2 mils.

En la imagen de la izquierda, se ve que la mayor parte de la corriente de retorno se desvía alrededor del espacio en el plano de referencia L2. En la imagen de la derecha, cuando la señal pasa a través del espacio, la mayor parte de la corriente de retorno fluye hacia el plano de referencia L3 debajo de la línea de transmisión, pero aún queda algo de corriente cerca del espacio en L2, lo que irradia algo de ruido.

Desde la perspectiva de la integridad de la señal, las señales reflejadas y el ruido de diafonía en el extremo cercano se han reducido esencialmente a la mitad, como se muestra en la Figura 15. Hay menos atenuación en el tiempo de subida de la señal transmitida y la diafonía en el extremo lejano también se ha mejorado. .

Volviendo a la pregunta principal, ¿qué perspectiva es la correcta? Ninguna de las dos cosas es del todo correcta. Este artículo analiza varios escenarios de líneas microstrip que pasan por planos divididos. Desde la perspectiva de la integridad de la señal, bajo ciertas condiciones, puede ser aceptable que las líneas microstrip pasen a través de planos divididos. Por ejemplo, en la simulación anterior, siempre que el espacio entre los planos divididos se reduzca a 5 mil y se agregue una fina capa dieléctrica entre las capas de los planos adyacentes, la diafonía no aumenta significativamente. Según las tolerancias de ruido reales, es posible que esto no tenga ningún impacto.

Sin embargo, desde la perspectiva de EMC, todavía existen más riesgos y preocupaciones. Nunca existe un escenario en el que alguna corriente de retorno nunca fluya hacia el borde del espacio del plano dividido, por lo que todavía existe el riesgo de EMI. Debido a la multitud de factores interrelacionados en los diseños reales, es un desafío tener una regla universal aplicable aquí o en cualquier otra situación.

Generalmente, las líneas microstrip deben evitar cruzar planos divididos. Sin embargo, cuando no sea posible realizar un análisis detallado del diseño real y de la colocación de las placas, se pueden explorar métodos alternativos para mitigar la radiación de ruido, como agregar blindaje externo adicional.

En última instancia, este artículo enfatiza que en los diseños modernos de alta velocidad, no podemos limitarnos a considerar solo la integridad de la señal, la integridad de la potencia o la EMC individualmente. Los tres deben considerarse simultáneamente. Si solo consideramos la integridad de la señal sin consideraciones de EMC, podemos sacar conclusiones incorrectas, lo que conduciría a posibles fallas en las pruebas de compatibilidad de EMC del producto final.