Nota dell'editore: nei moderni progetti ad alta velocità, analizzare separatamente l'integrità del segnale, l'integrità dell'alimentazione e la compatibilità elettromagnetica non è sufficiente; un approccio olistico è essenziale per una progettazione di successo.

Problema di fondo: quando i segnali attraversano aree di segmentazione tra piani di riferimento adiacenti su uno strato, spesso sorgono discussioni sull'integrità del segnale. Alcuni sostengono che i segnali non dovrebbero attraversare la segmentazione poiché ciò potrebbe aumentare i problemi di diafonia e di compatibilità elettromagnetica, mentre altri suggeriscono che con un'attenta progettazione dello stackup dei livelli e dell'ampiezza degli spazi di segmentazione sui piani di alimentazione/massa, non dovrebbero esserci problemi. Allora, qual è l'approccio giusto? Naturalmente, la risposta migliore è “dipende!” Questo articolo esplora lo scenario in cui i segnali passano attraverso piani segmentati.

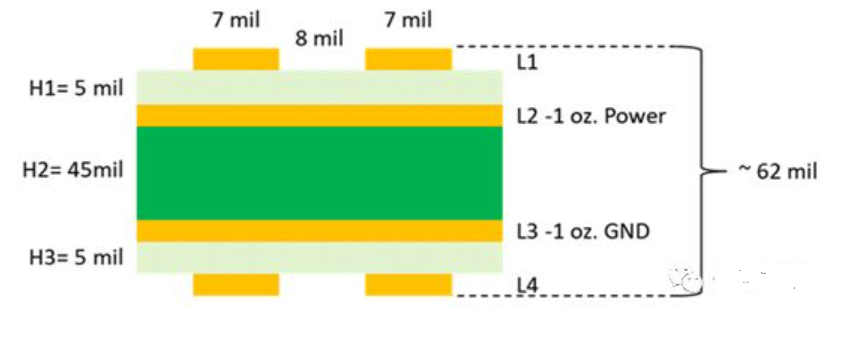

Innanzitutto, consideriamo un tipico PCB a quattro strati stackup con uno spessore totale di 62 mil. Lo strato superficiale è lo strato del segnale, mentre gli strati interni sono gli strati piani. La larghezza della traccia è di 7/8 mil, con un'impedenza differenziale di 100 ohm e un'impedenza single-ended di 56 ohm.

Nella moderna progettazione di prodotti elettronici, è abbastanza comune avere più binari di alimentazione in un prodotto, il che significa che il piano di alimentazione in una scheda a quattro strati sarà inevitabilmente diviso. Pertanto, la presenza di incroci di segnale sugli split è inevitabile durante il routing.

Supponendo che una coppia di linee di trasmissione superficiali attraversino uno spazio largo 50 mil tra strati adiacenti, come mostrato nella figura, viene illustrata la sezione trasversale della linea a microstriscia prima e dopo il passaggio attraverso lo spazio. Viene considerato lo spessore dielettrico H1 dalla superficie allo strato di riferimento di potenza adiacente. Poiché non ci sono piani di riferimento di potenza adiacenti nel gap, e il piano di riferimento successivo è il terreno adiacente allo strato inferiore, lo spessore dielettrico nel gap è uguale a H1 più lo spessore dello strato di potenza da 1 oncia, più lo strato dielettrico successivo H2. Se lo spessore dello strato di potenza è 1.2 mil, lo spessore dielettrico totale in corrispondenza dell'intercapedine è 51.2 mil.

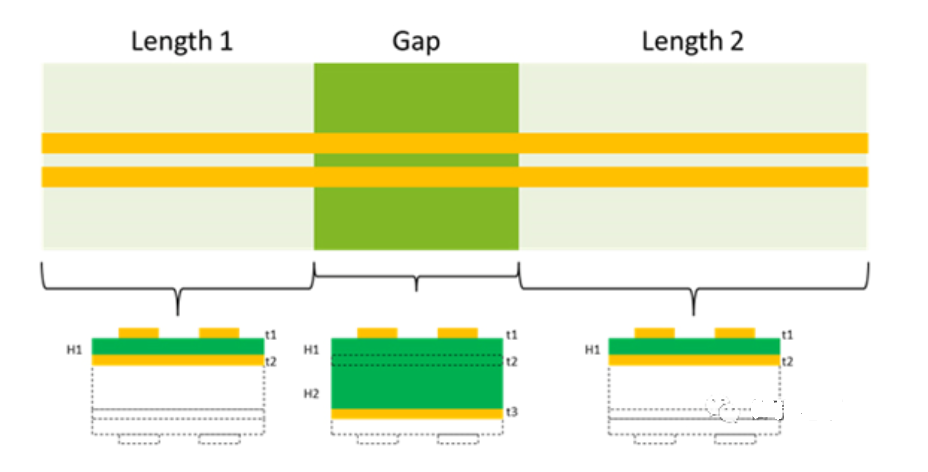

L'approssimazione del primo ordine di questa topologia è una combinazione di tre segmenti di linee di trasmissione con due diverse impedenze. Il primo e l'ultimo segmento hanno entrambi un'impedenza differenziale di 100 ohm e un'impedenza single-ended di 56 ohm, mentre la linea di trasmissione nella parte interstiziale ha un'impedenza differenziale di 134 ohm e un'impedenza single-ended di 103 ohm. La sua impedenza è più alta rispetto ad altre parti, causando qui la riflessione del segnale. L'altezza e la larghezza della riflessione sono funzioni del corrispondente tempo di salita del segnale e della geometria del gap. Più veloce è il tempo di salita e più ampio è il divario, maggiore è la riflessione causata. La Figura 3 mostra i risultati della simulazione.

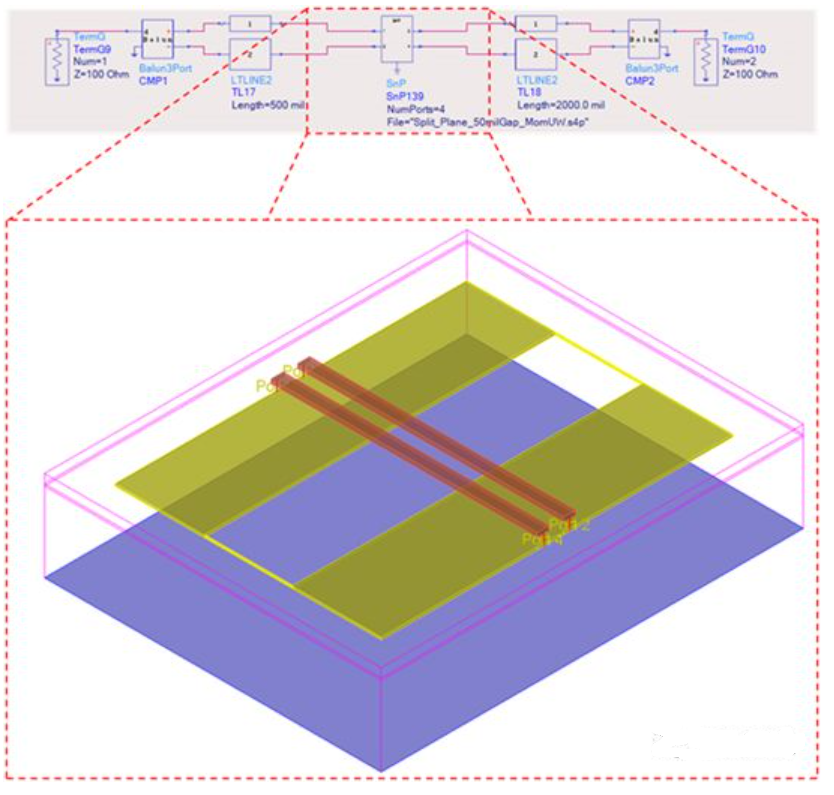

Il primo e il terzo segmento delle linee di trasmissione vengono simulati utilizzando il modello 2D di TLines-LineType (ADS), mentre la linea di trasmissione in corrispondenza del gap viene simulata utilizzando un solutore di campo elettromagnetico 3D (Momentum o EMPro) per ottenere gli effetti del campo elettromagnetico quando il passa il segnale. I materiali dielettrici sono gli stessi. I parametri S vengono estratti e utilizzati nello schema.

La lunghezza totale della topologia è di 2.65 pollici, con la lunghezza del primo segmento della linea di trasmissione (L1) di 500 mil e la lunghezza del terzo segmento (L2) di 2 pollici. La parte 3D è divisa in tre segmenti da 50 mil ciascuno per facilitare la regolazione della larghezza dello spazio garantendo allo stesso tempo che la lunghezza totale rimanga invariata.

Vengono utilizzate due larghezze di gap per confrontare gli effetti della dimensione del gap. Un divario di 50 milioni tra gli aerei a motore è comune e rappresenta lo scenario peggiore. Uno spazio di 5 mil è lo scenario ottimale ed è anche il valore minimo tipico dalla linea di trasmissione al pad di saldatura.

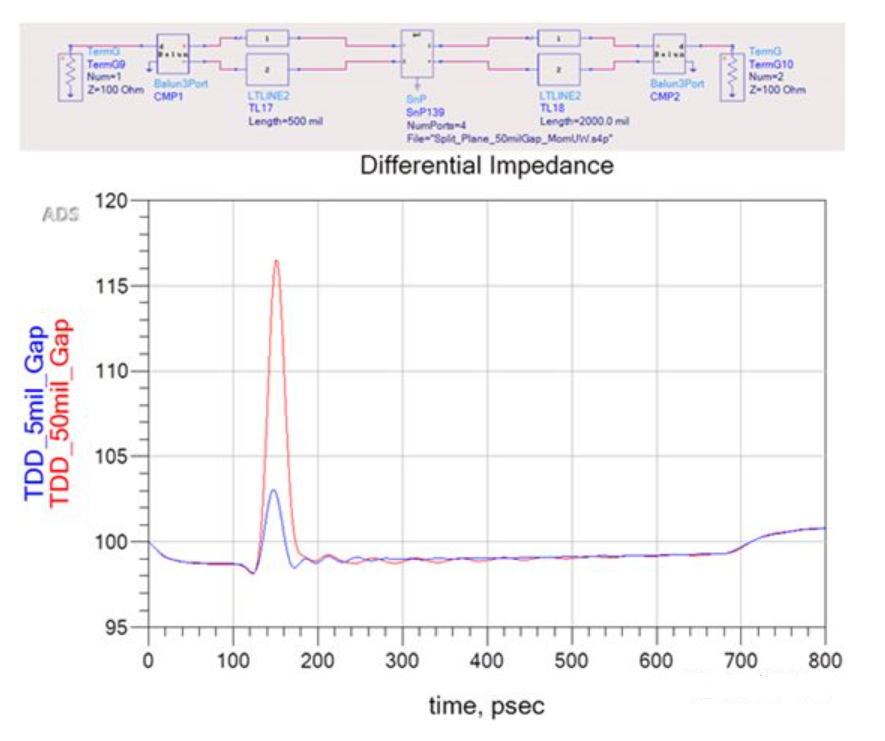

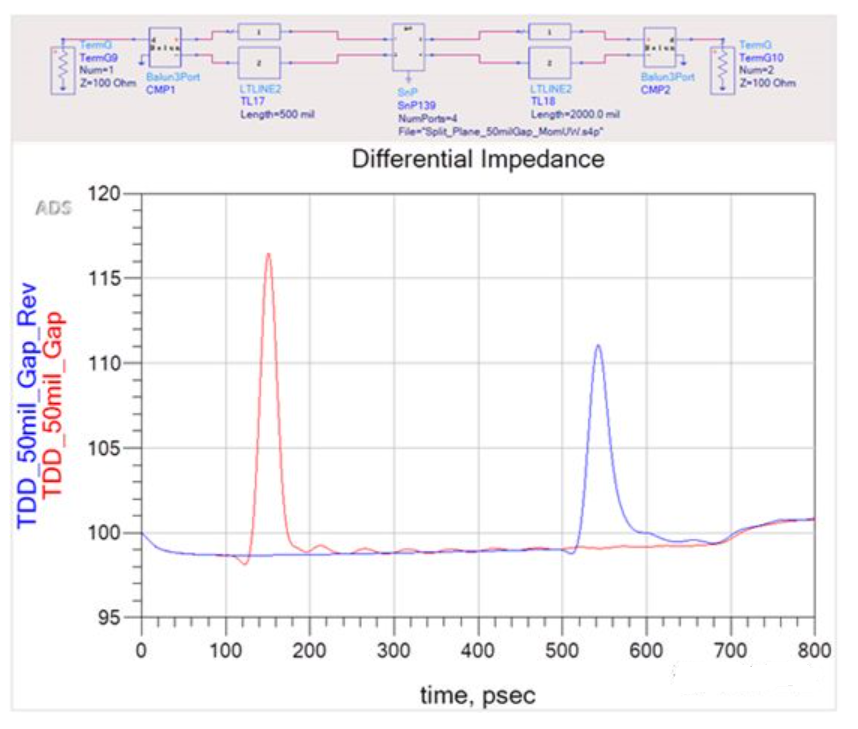

Una sorgente di eccitazione differenziale viene applicata alla porta 1 e il confronto delle impedenze differenziali è mostrato nella Figura 4. Per facilitare la visualizzazione dell'impedenza alla porta 2, viene utilizzato un convertitore balun per convertire la porta 4 alla porta 2. La curva rossa rappresenta i risultati per un intervallo di 50 mil, che mostra una maggiore discontinuità di impedenza rispetto ai risultati per un intervallo di 5 mil (curva blu). Questo perché l'altezza dell'impulso emesso è determinata sia dal tempo di salita che dall'ampiezza del gap. Poiché il tempo di salita è inferiore in lunghezza spaziale rispetto alla larghezza del gap, la sola modifica del tempo di salita non può raggiungere la massima discontinuità di impedenza. Ciò sarà dimostrato attraverso la simulazione di seguito.

Una sorgente di eccitazione viene applicata alla porta 2, con un intervallo di 50 mil, e confrontata con il segnale di ingresso dalla porta 1, come mostrato nella figura seguente. A causa di un ritardo di 2.05 pollici prima dell'intervallo, insieme alle perdite nella linea di trasmissione, il fronte del segnale sarà più lento. Come previsto, l'ampiezza della riflessione è effettivamente inferiore.

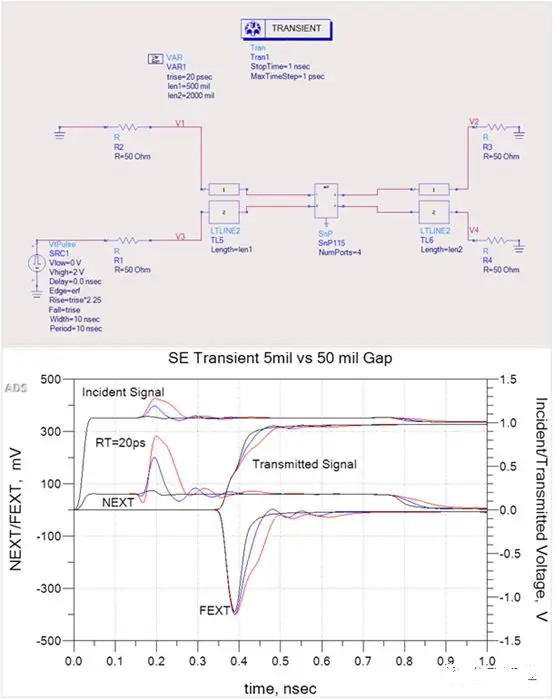

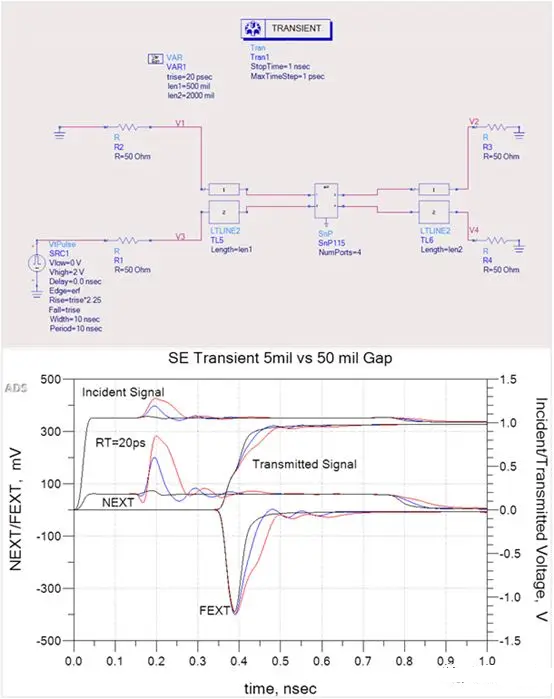

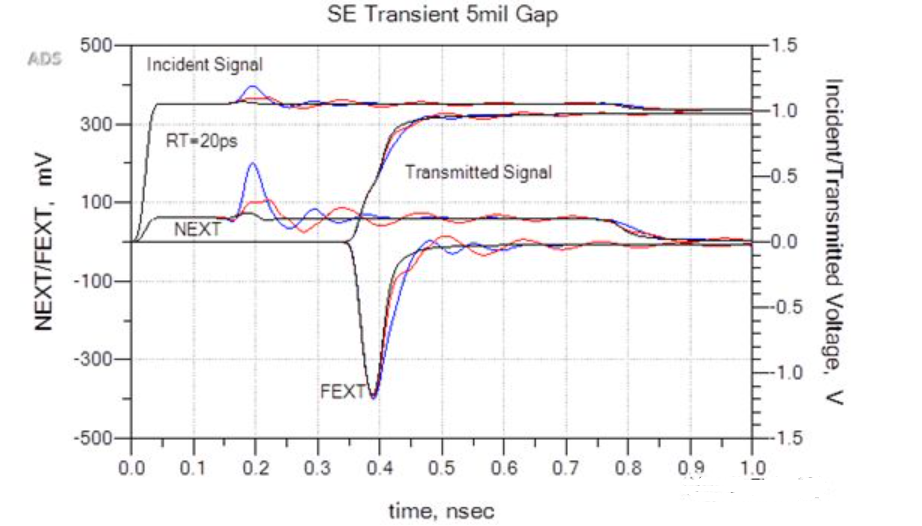

Ecco l'analisi del caso single-ended, come mostrato in figura. La curva rossa rappresenta un divario di 50 mil, la curva blu rappresenta un divario di 5 mil e la curva nera non rappresenta alcun divario. Con un tempo di salita di 20 ps, la tensione di riflessione è massima quando il gap è di 50 mil, con conseguente leggero aumento del ritardo della linea di trasmissione rispetto al caso senza gap.

In tutti e tre gli scenari, si possono osservare le tipiche variazioni della curva di diafonia Near-End e Far-End. Lo stretto accoppiamento tra le linee di trasmissione attraverso l'intercapedine determina riflessioni più elevate, portando a una maggiore diafonia prossimale.

Ecco l'analisi del caso single-ended, come mostrato in figura. La curva rossa rappresenta un divario di 50 mil, la curva blu rappresenta un divario di 5 mil e la curva nera non rappresenta alcun divario. Con un tempo di salita di 20 ps, la tensione di riflessione è massima quando il gap è di 50 mil, con conseguente leggero aumento del ritardo della linea di trasmissione rispetto al caso senza gap.

In tutti e tre gli scenari, si possono osservare le tipiche variazioni della curva di diafonia Near-End e Far-End. Quando si passa attraverso lo spazio vuoto, lo stretto accoppiamento tra le linee di trasmissione provoca riflessioni più elevate, portando a una maggiore diafonia prossimale.

Quando c'è un intervallo di 50 mil, gli impulsi di crosstalk vicini aumentano in modo significativo, mentre il crosstalk lontano aumenta solo leggermente. A differenza della tensione di diafonia del punto vicino, il valore di picco della tensione di diafonia del punto lontano varia con la lunghezza dell'accoppiamento. Ad un certo ritardo temporale (TD), la sua ampiezza raggiunge il picco a circa il 50% del tempo di salita del segnale della linea attaccante.

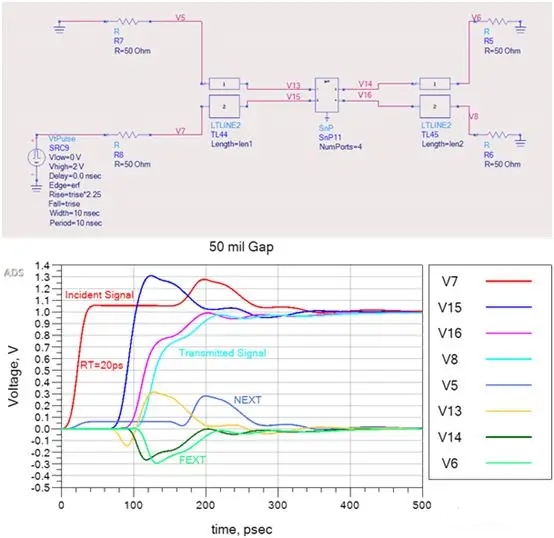

Allo stesso modo, il segnale proveniente dalla linea di attacco si accoppia alla tensione di diafonia dell'estremità lontana, che si accoppia nuovamente alla linea di attacco, influenzando il tempo di salita. La forma d'onda all'estremità della linea di attacco è la sovrapposizione della tensione di diafonia dell'estremità lontana e della tensione del segnale originale, con conseguente assenza di diafonia. Poiché l'estremità lontana è a 2.65 pollici di distanza dall'estremità sorgente, la diafonia remota è prossima alla saturazione. Riducendo la lunghezza dell'ultimo segmento della linea di trasmissione a 100 mil, come mostrato nella Figura 7, è più semplice comprendere l'impatto del gap sulla diafonia far-end.

La curva rossa rappresenta il segnale di ingresso (V7) con un tempo di salita di 20 ps, la curva ciano (V8) rappresenta la forma d'onda del segnale trasmesso all'estremità lontana, l'azzurro (V5) rappresenta la diafonia vicina, il verde chiaro ( V6) rappresenta la diafonia remota e il verde scuro (V15) rappresenta il segnale di attacco sul nodo V13 dopo aver attraversato TL44. A causa dell'elevata impedenza nella sezione gap, su questo segmento della linea di trasmissione si può osservare una sovraelongazione causata da maggiori riflessioni.

La forma d'onda arancione (V13) mostra impulsi di diafonia negativi all'estremità lontana, coerenti con il fronte di salita del segnale di attacco su V15. Anche la diafonia di prossimità si allinea con la riflessione positiva su V15. Poiché il segnale di attacco subisce un ritardo quando passa attraverso lo spazio vuoto, l'ulteriore oscillazione di tensione della riflessione aumenta l'ampiezza degli impulsi di diafonia all'estremità lontana e la sua forma invertita riflette la forma dell'impulso riflesso, come si vede nella forma d'onda verde scuro ( V14), che poi si accoppia nuovamente al segnale di attacco e fa decadere il tempo di salita fino all'uscita dalla sezione di accoppiamento, come mostrato dalla curva magenta (V16).

Il problema affrontato in questo articolo è che quando un segnale passa attraverso un piano segmentato, il segnale trasmesso subisce riflessioni positive e negative a causa di disadattamenti di impedenza, con il tempo di riflessione pari al tempo necessario per passare attraverso lo spazio vuoto. Ciò aumenta l'ampiezza del segnale e degli impulsi di diafonia del far-end, rallentando così il tempo di salita del segnale trasmesso in proporzione alla forma d'onda del crosstalk del far-end.

Tenendo conto di molteplici percorsi di ritorno sul piano segmentato e sui bordi, si forma un'efficace antenna a fessura, che irradia il rumore verso l'esterno. Per soddisfare i requisiti di radiazione EMI FCC Classe B (campo di 3 metri), il rumore irradiato deve essere inferiore a 100 mV/m tra 30 e 80 MHz e inferiore a 200 mV/m tra 216 MHz e 1 GHz.

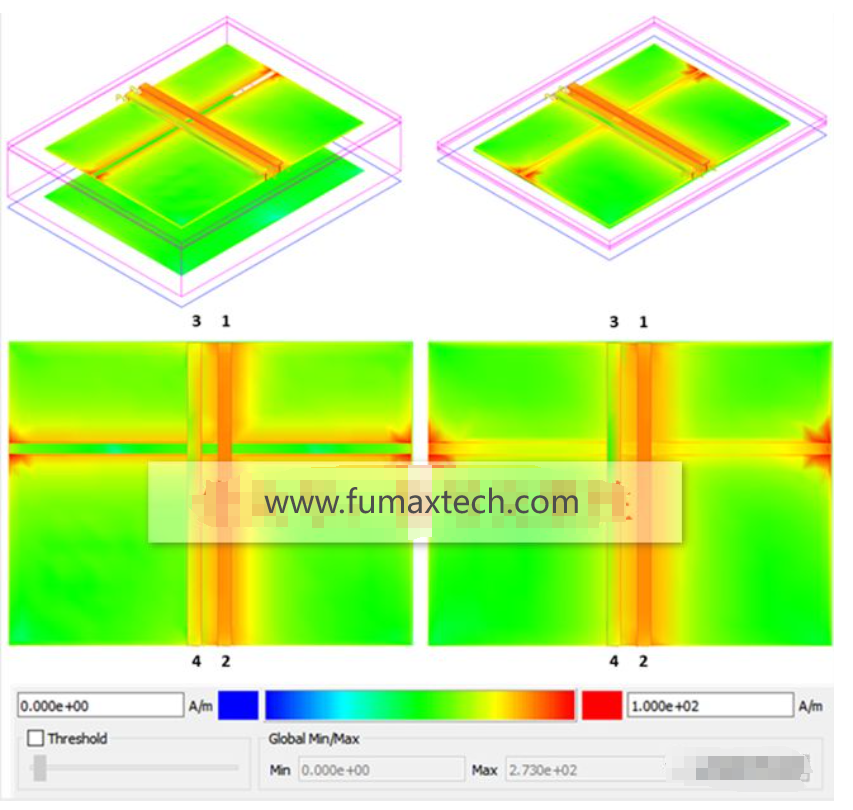

Quando le linee a microstriscia attraversano piani segmentati, il rumore può irradiarsi nello spazio libero a causa dei percorsi di ritorno discontinui e della mancanza di schermatura. La visualizzazione della densità della corrente di ritorno nello spazio tra piani di riferimento adiacenti può essere ottenuta tramite un software di simulazione 3D.

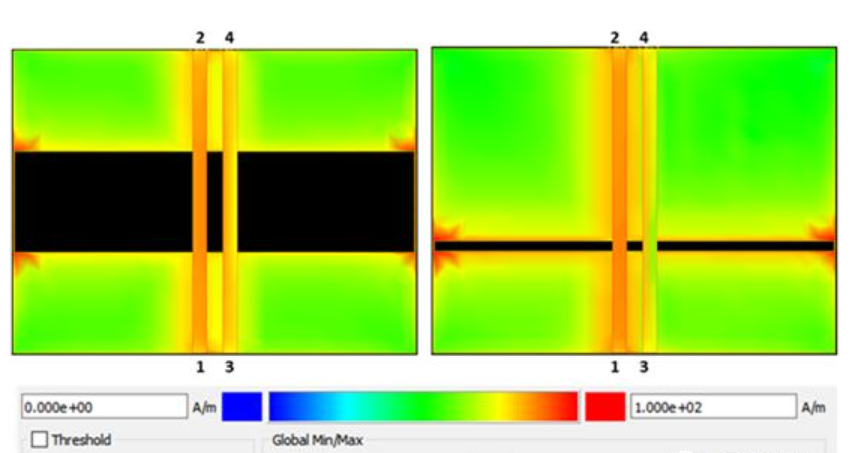

La Figura 8 confronta la densità di corrente di ritorno del segnale single-ended su piani di riferimento adiacenti. A sinistra, un'onda sinusoidale da 4 GHz passa attraverso un gap di 50 mil, mentre a destra passa attraverso un gap di 5 mil. La scelta di un segnale a 4 GHz è dovuta al fatto che rappresenta la frequenza Nyquist di 8 Gbps PCIe Gen 3 su una tipica scheda PCIe a 4 strati. Guidando il segnale dalla porta 1 alla porta 2 con le porte 3 e 4 adeguatamente terminate, è possibile osservare chiaramente la distribuzione della densità di corrente di ritorno sul piano di riferimento in corrispondenza della segmentazione.

Si noti il leggero aumento della densità di corrente ai bordi dello spazio dove si trova la linea vittima. Ciò indica che la corrente di ritorno sulle linee adiacenti provoca ulteriore tensione di diafonia all'estremità lontana, come discusso in precedenza. Da questo punto di vista, le linee single-ended che attraversano la segmentazione potrebbero non rappresentare un approccio ottimale.

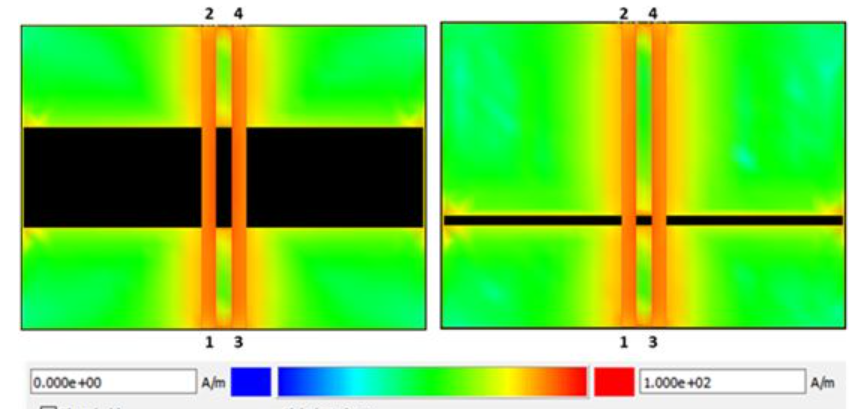

La Figura 9 mostra la densità della corrente di ritorno sul piano di riferimento quando un segnale differenziale da 4 GHz passa attraverso intervalli di 50 mil (a sinistra) e 5 mil (a destra). Si può osservare che la massima densità di corrente tra le due coppie differenziali è concentrata ai bordi della segmentazione, con solo una piccola porzione che si propaga lungo l'intercapedine.

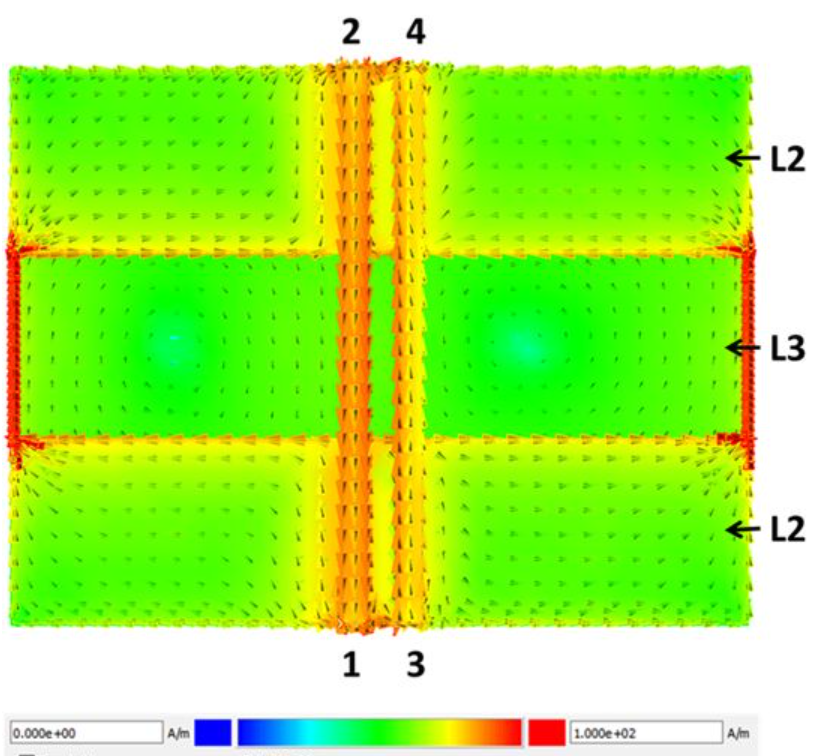

Quando un segnale single-ended viene immesso dalla porta 1 alla porta 2, con le altre porte terminate, la Figura 10 mostra la direzione delle correnti sugli strati piani L2 e L3. Si può osservare che quando la direzione della corrente va dalla porta 2 alla porta 1, la corrente di ritorno su L2 è divisa in due parti all'estremità dell'intercapedine (lato porta 1). Inoltre, ci sono due correnti a rotazione inversa su L3, concentrate principalmente nelle metà sinistra e destra dello spazio vuoto. Questi sono causati da correnti a rotazione inversa lungo il bordo dello spazio su L2 che iniettano energia EM nella cavità piana. È interessante notare che la direzione delle correnti rotanti su L2 e L3 è opposta.

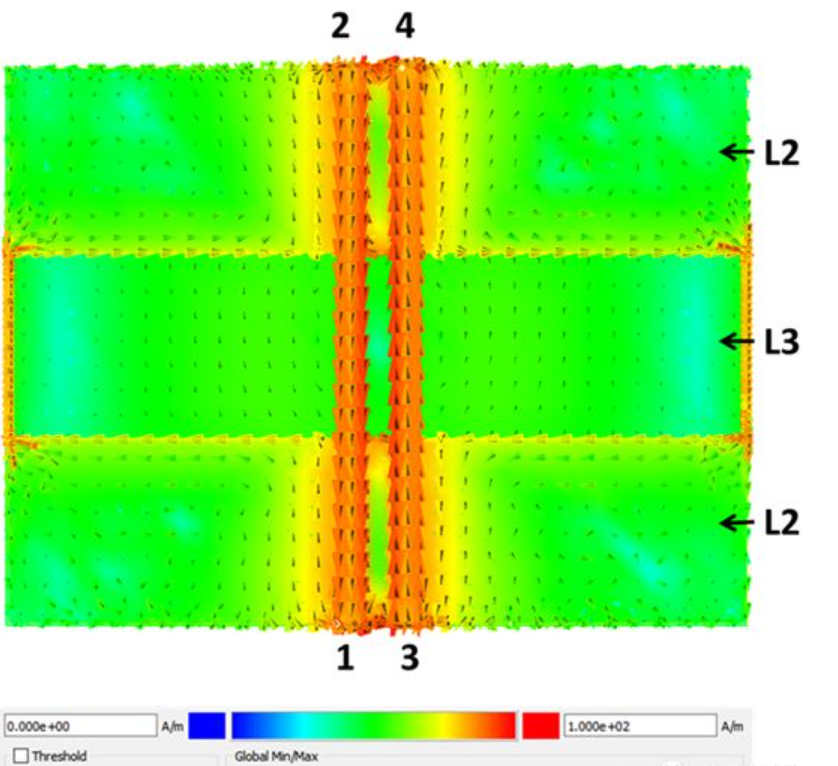

Tuttavia, quando si applica un segnale differenziale alle due linee di trasmissione, come mostrato in Figura 11, si può osservare che la direzione della corrente lungo il bordo dell'intercapedine è la stessa. È inoltre importante notare che la corrente rotante su L3 è unidirezionale, concentrata tra le coppie differenziali e il gap. Il problema qui è che anche quando viene applicato un segnale differenziale alle due linee di trasmissione, c'è ancora corrente che scorre verso il bordo dello spazio vuoto, introducendo rumore nella cavità piana e irradiandosi nello spazio libero, causando EMI.

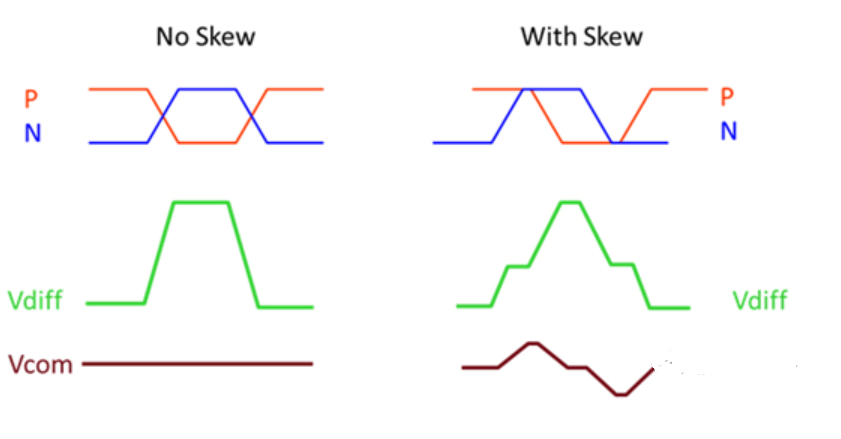

Nell'analisi precedente, l'esempio di una coppia differenziale presupponeva una perfetta corrispondenza interna, ma in realtà tali casi sono rari. Fattori come lunghezze di instradamento disuguali, effetti fibra di vetro, differenze nella lunghezza dei pin del connettore o asimmetria nei via differenziali quando si cambiano gli strati possono portare a disadattamenti del ritardo interno. Quando si verificano queste situazioni, alcuni segnali di modo comune possono essere convertiti in segnali di modo differenziale. Come mostrato nella Figura 12, il grado di conversione dipende dalla mancata corrispondenza del ritardo interno. In una coppia differenziale ideale, Vdiff rappresenta la differenza di tensione tra i segnali P e N. Se la loro differenza di fase è di 180 gradi, la tensione di modo comune raddoppierà e non ci sarà tensione di modo comune. Tuttavia, in caso di disallineamento, la differenza di fase della coppia differenziale non è di 180 gradi. Considerando la distorsione, il segnale differenziale si deformerà, risultando in una tensione di modo comune (Vcom). L'entità e la forma della tensione di modo comune sono proporzionali allo sfasamento. Se le fasi di P e N sono identiche, non c'è tensione differenziale e tutta diventa tensione di modo comune. La tensione di modo comune richiede anche un percorso di ritorno e, se il percorso viene interrotto, la sua corrente di ritorno passerà attraverso il piano diviso in modo simile alle correnti di ritorno a terminazione singola.

Secondo alcune specifiche di cablaggio PCIe, l'inclinazione nel caso peggiore è 0.21UI (un'interfaccia utente rappresenta il tempo di un bit). A PCIe Gen3 8Gbps, un offset di 0.21UI corrisponde a 26.3ps. Lo scenario che passa attraverso un gap di 50mil equivale ad uno sfasamento interno, come mostrato nella Figura 13, rispetto alla situazione ideale. Come previsto, la tensione di modo comune passa attraverso il piano di partizione e la corrente di ritorno di modo comune è simile alla situazione con linee a terminazione singola che passano attraverso il piano di partizione (Figura 8). L'unica differenza è che non esiste una corrente di modo comune al 100%, quindi ci sarà anche una corrente di ritorno di modo differenziale.

L’ultima questione da affrontare è che se è presente uno strato dielettrico estremamente sottile tra lo strato di terra adiacente e lo strato di potenza partizionato, fungerà da percorso di ritorno migliore quando si passa attraverso lo strato partizionato. Logicamente, questo ha senso dal punto di vista dell'integrità del segnale, poiché l'impedenza delle linee di trasmissione diminuisce con l'aumento dello spessore dielettrico tra la linea di trasmissione e il piano di riferimento partizionato.

Negli esempi precedenti abbiamo ipotizzato un pannello a quattro strati con uno spessore di 62 mil. Ciò determina quasi lo spessore dello strato dielettrico interno nella pila. Per spostare il piano di riferimento più vicino allo spazio tra i piani di potenza, il numero di strati del PCB deve essere aumentato ad almeno 6 strati per mantenere la simmetria dello stack e lo spessore totale.

Se lo spessore del dielettrico sotto lo spazio viene ridotto, simulando nuovamente lo spazio di 5 mil, nel caso single-ended, i risultati sono mostrati nella Figura 14. Questo strato dielettrico sottile è impostato su 2 mil, che è uno spessore comune per il disaccoppiamento nuclei di capacità sepolti sul piano di potenza. Aggiungendo lo spessore di 5 mil per H1 e 1.2 mil per il piano di potenza L2, come mostrato nella Figura 1, lo spessore dielettrico totale sotto lo spazio vuoto è 8.2 mil.

Nell'immagine a sinistra, si vede che la maggior parte della corrente di ritorno viene deviata attorno allo spazio vuoto nel piano di riferimento L2. Nell'immagine a destra, quando il segnale passa attraverso l'intercapedine, la maggior parte della corrente di ritorno fluisce verso il piano di riferimento L3 sotto la linea di trasmissione, ma una parte di corrente rimane ancora vicino all'intercapedine in L2, irradiando così un po' di rumore.

Dal punto di vista dell'integrità del segnale, i segnali riflessi e il rumore della diafonia vicina sono stati sostanzialmente dimezzati, come mostrato nella Figura 15. C'è meno attenuazione nel tempo di salita del segnale trasmesso e anche la diafonia lontana è stata migliorata .

Tornando alla domanda principale, quale prospettiva è corretta? Nessuno dei due è del tutto corretto. Questo articolo discute diversi scenari di linee a microstriscia che passano attraverso piani divisi. Dal punto di vista dell'integrità del segnale, in determinate condizioni, può essere accettabile che le linee a microstriscia passino attraverso piani divisi. Ad esempio, nella simulazione di cui sopra, finché lo spazio tra i piani divisi viene ridotto a 5 mil e viene aggiunto un sottile strato dielettrico tra gli strati piani adiacenti, la diafonia non aumenta in modo significativo. In base alle effettive tolleranze sul rumore, ciò potrebbe non avere alcun impatto.

Tuttavia, dal punto di vista EMC, esistono ancora più rischi e preoccupazioni. Non esiste mai uno scenario in cui parte della corrente di ritorno non fluisca mai fino al bordo del gap del piano diviso, quindi esiste ancora il rischio di EMI. A causa della moltitudine di fattori interconnessi nei progetti reali, è difficile avere una regola universale applicabile qui o in qualsiasi altra situazione.

In generale, le linee a microstriscia dovrebbero evitare di attraversare piani divisi. Tuttavia, quando non è possibile effettuare un'analisi dettagliata del layout effettivo e dell'impilamento delle schede, è possibile esplorare metodi alternativi per mitigare la radiazione acustica, come l'aggiunta di un'ulteriore schermatura esterna.

In definitiva, questo articolo sottolinea che nei moderni progetti ad alta velocità non possiamo limitarci a considerare singolarmente solo l'integrità del segnale, l'integrità dell'alimentazione o la compatibilità elettromagnetica. Tutti e tre devono essere considerati contemporaneamente. Se consideriamo solo l'integrità del segnale senza considerazioni sulla compatibilità elettromagnetica, potremmo trarre conclusioni errate, portando a potenziali fallimenti nei test di compatibilità EMC del prodotto finale.