編集者注: 最新の高速設計では、シグナル インテグリティ、パワー インテグリティ、EMC を個別に分析するだけでは十分ではありません。デザインを成功させるには、総合的なアプローチが不可欠です。

背景問題: 信号がレイヤー上の隣接する基準面間のセグメンテーション領域を越える場合、信号の完全性に関する議論が頻繁に発生します。クロストークやEMCの問題が増加する可能性があるため、信号がセグメンテーションを越えるべきではないと主張する人もいますが、層の積層と電源/グランドプレーンのセグメンテーションギャップの幅を慎重に設計すれば問題は起こらないはずだと主張する人もいます。では、正しいアプローチは何でしょうか?もちろん、最良の答えは「それは状況による!」です。この記事では、信号がセグメント化されたプレーンを通過する場合のシナリオについて説明します。

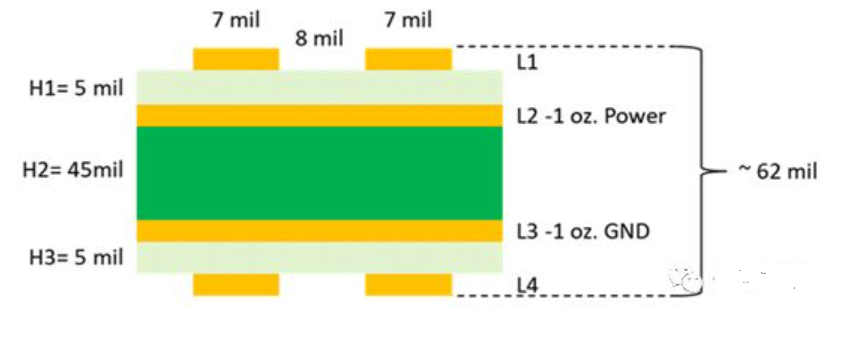

まず、典型的なものを考えてみましょう 4層PCB 総厚さ62ミルのスタックアップ。表層は信号層であり、内部層はプレーン層です。トレース幅は 7/8 ミル、差動インピーダンスは 100 オーム、シングルエンド インピーダンスは 56 オームです。

現代の電子製品設計では、製品内に複数の電源レールを搭載することが非常に一般的です。これは、4 層基板内の電源プレーンが必然的に分割されることを意味します。したがって、配線中にスプリットをまたぐ信号の存在は避けられません。

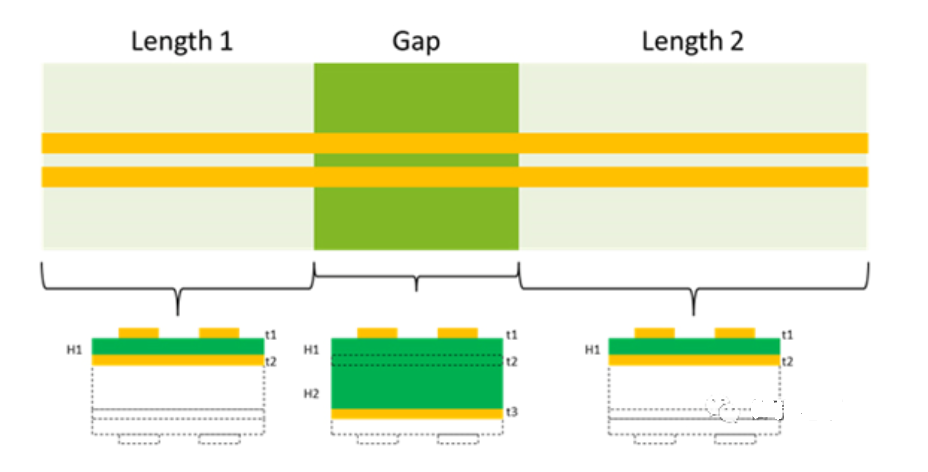

図に示すように、一対の表面伝送線路が隣接する層間の幅 50 ミルのギャップを横切ると仮定し、ギャップを通過する前後のマイクロストリップ線路の断面を示します。表面から隣接する電力基準層までの誘電体の厚さ H1 が考慮されます。ギャップには隣接する電源基準面がなく、次の基準面は最下層に隣接するグランドであるため、ギャップの誘電体の厚さは、H1 に 1oz の電源層の厚さを加えたものに次の誘電体層を加えたものと等しくなります。 H2.電源層の厚さが 1.2 ミルの場合、ギャップにおける誘電体の総厚は 51.2 ミルになります。

このトポロジの一次近似は、100 つの異なるインピーダンスを持つ伝送線路の 56 つのセグメントの組み合わせです。最初と最後のセグメントは両方とも差動インピーダンス 134Ω、シングルエンド インピーダンス 103Ωですが、ギャップ部分の伝送線路は差動インピーダンス 3Ω、シングルエンド インピーダンス XNUMXΩです。他の部分に比べてインピーダンスが高いため、ここで信号の反射が発生します。反射の高さと幅は、対応する信号の立ち上がり時間とギャップの形状の関数です。立ち上がり時間が速く、ギャップが広いほど、発生する反射は大きくなります。図 XNUMX にシミュレーション結果を示します。

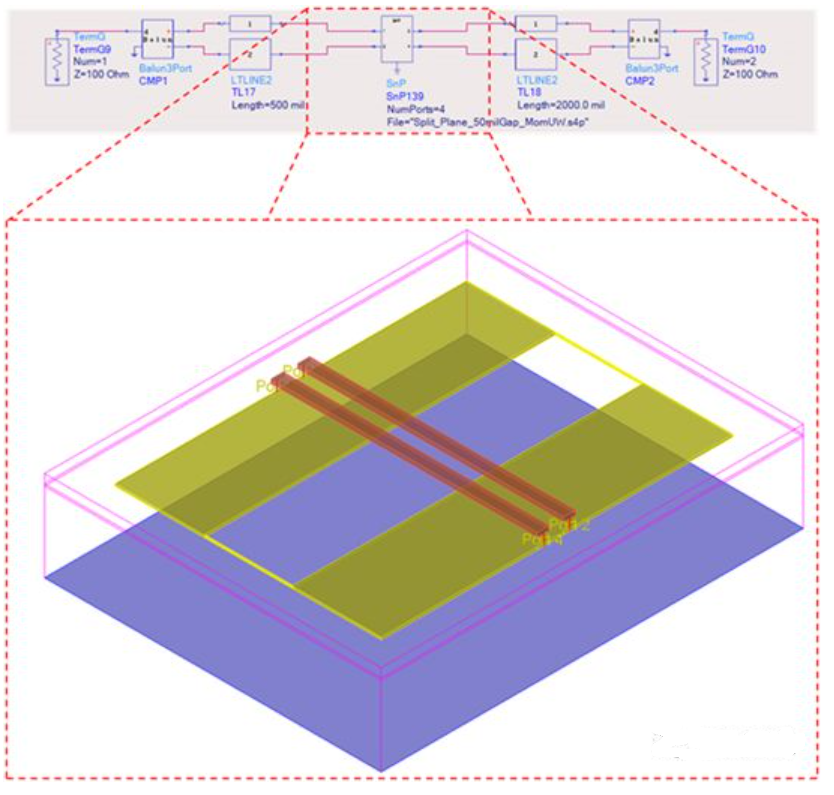

伝送線路の 2 番目と 3 番目のセグメントは TLines-LineType (ADS) の XNUMXD モデルを使用してシミュレートされ、ギャップの伝送線路は XNUMXD 電磁場ソルバー (Momentum または EMPro) を使用してシミュレートされ、信号が通過します。誘電体材料は同じです。 S パラメータが抽出され、回路図で使用されます。

トポロジの全長は 2.65 インチで、伝送線路の最初のセグメント (L1) の長さは 500 ミル、2 番目のセグメント (L2) の長さは 3 インチです。 50D パーツは、全長を変えずにギャップ幅の調整を容易にするために、それぞれ XNUMX ミルの XNUMX つのセグメントに分割されています。

ギャップ サイズの効果を比較するために 50 つのギャップ幅が使用されます。電源プレーン間のギャップは 5 mil であるのが一般的であり、最悪のシナリオを表します。 XNUMX ミルのギャップが最適なシナリオであり、伝送線路からはんだパッドまでの一般的な最小値でもあります。

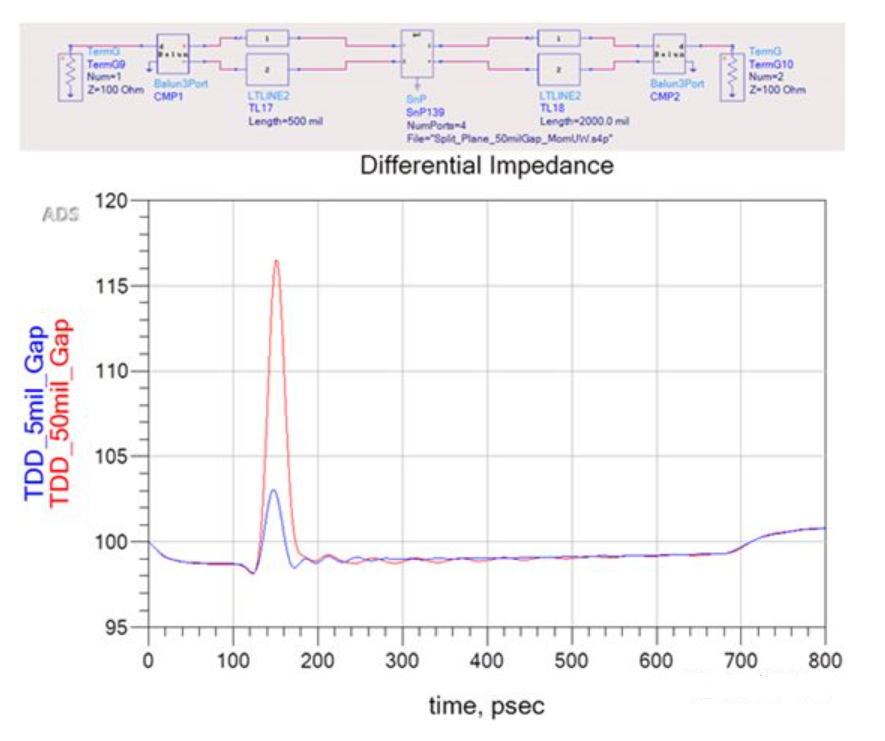

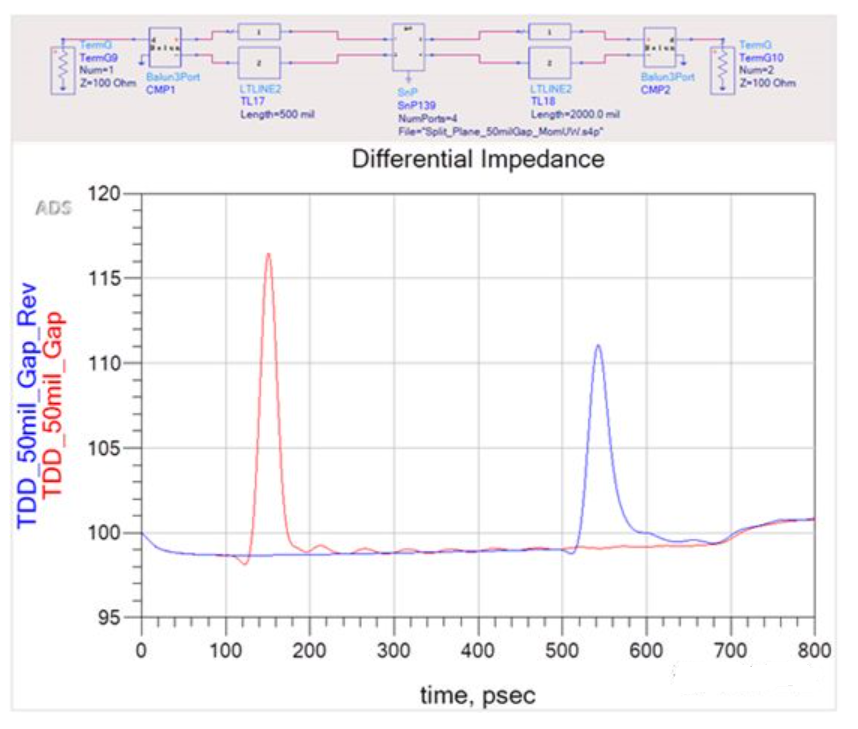

差動励起源がポート 1 に適用され、差動インピーダンスの比較が図 4 に示されています。ポート 2 でのインピーダンスを見やすくするために、バラン コンバータを使用してポート 4 をポート 2 に変換します。赤い曲線は結果を表しています。 50 ミルのギャップの場合、5 ミルのギャップの結果 (青い曲線) と比較して、より高いインピーダンスの不連続性が示されます。これは、放射されるパルスの高さが立ち上がり時間とギャップ幅の両方によって決まるためです。立ち上がり時間はギャップ幅に比べて空間長が小さいため、立ち上がり時間を変更するだけでは最大のインピーダンス不連続を達成することはできません。これについては、以下のシミュレーションを通じて実証します。

次の図に示すように、励振源が 2 ミルのギャップでポート 50 に適用され、ポート 1 からの入力信号と比較されます。ギャップの前の 2.05 インチの遅延と伝送ラインの損失により、信号のエッジは遅くなります。予想通り、反射の振幅は確かに低くなります。

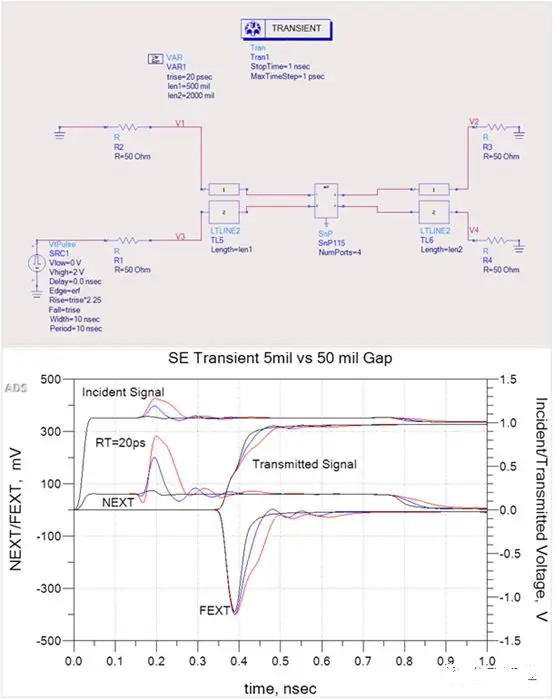

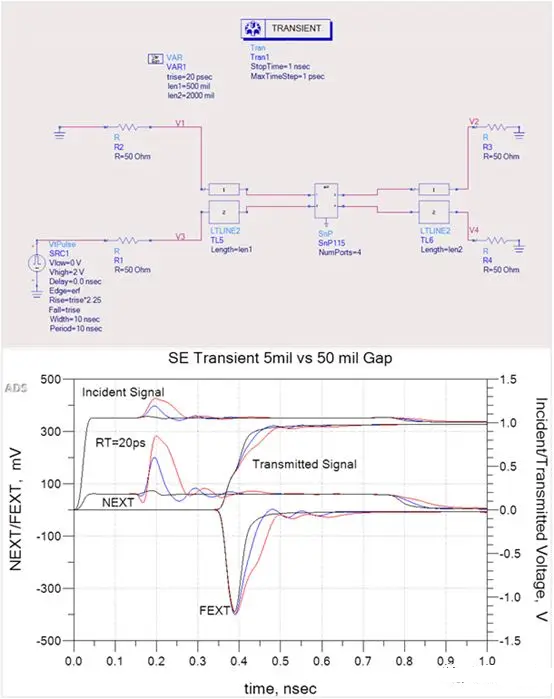

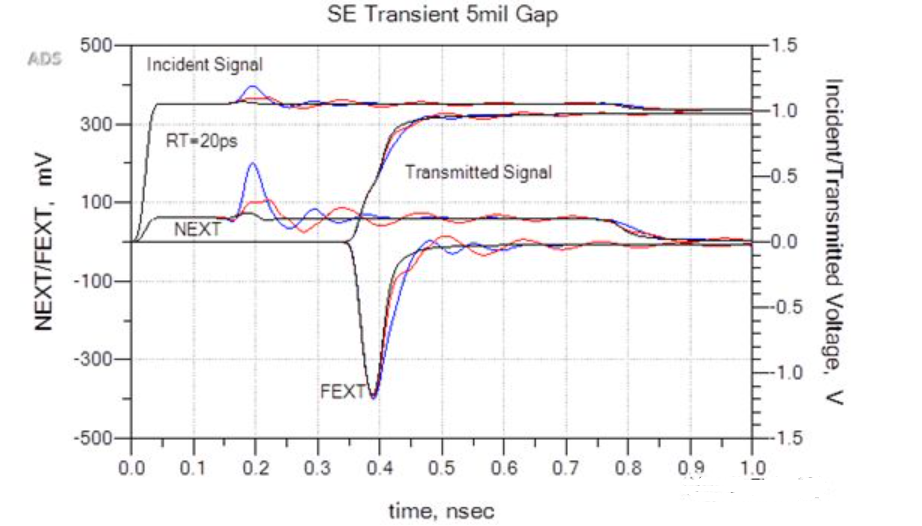

図に示すように、シングルエンドの場合の分析を次に示します。赤い曲線は 50 ミルのギャップを表し、青い曲線は 5 ミルのギャップを表し、黒い曲線はギャップがないことを表します。立ち上がり時間が 20 ps の場合、反射電圧はギャップが 50 mil のときに最も高く、その結果、ギャップがない場合と比較して伝送線遅延がわずかに増加します。

3 つのシナリオすべてで、典型的な近端クロストーク曲線と遠端クロストーク曲線の変化が観察されます。ギャップを介した伝送線路間の緊密な結合により、反射が増加し、近端クロストークが大きくなります。

図に示すように、シングルエンドの場合の分析を次に示します。赤い曲線は 50 ミルのギャップを表し、青い曲線は 5 ミルのギャップを表し、黒い曲線はギャップがないことを表します。立ち上がり時間が 20 ps の場合、反射電圧はギャップが 50 mil のときに最も高く、その結果、ギャップがない場合と比較して伝送線遅延がわずかに増加します。

3 つのシナリオすべてで、典型的な近端クロストーク曲線と遠端クロストーク曲線の変化が観察されます。ギャップを通過する際、伝送線路間の密結合により反射が増加し、近端クロストークが大きくなります。

50 ミルのギャップがある場合、近端のクロストーク パルスは大幅に増加しますが、遠端のクロストークはわずかしか増加しません。近端クロストーク電圧とは異なり、遠端クロストーク電圧のピーク値は結合長によって変化します。一定の時間遅延 (TD) が経過すると、その振幅は攻撃側のライン信号の立ち上がり時間の約 50% でピークになります。

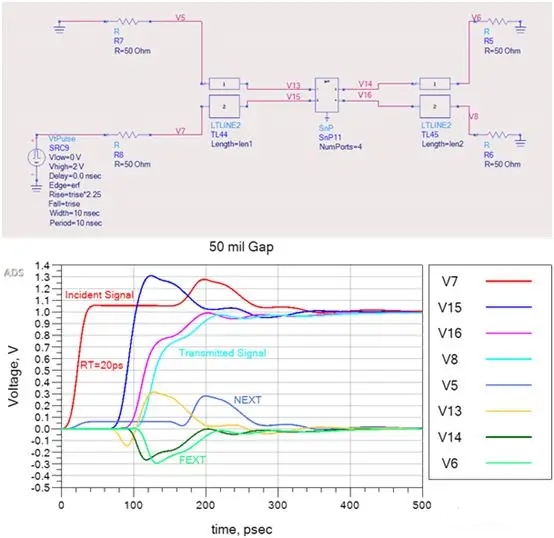

同様に、攻撃回線からの信号は遠端クロストーク電圧に結合し、それが攻撃回線に戻って結合し、立ち上がり時間に影響を与えます。攻撃回線の遠端の波形は、遠端クロストーク電圧と元の信号電圧が重畳されたものであるため、クロストークは発生しません。遠端はソース端から 2.65 インチ離れているため、遠端のクロストークは飽和に近づいています。図 100 に示すように、伝送線路の最後のセグメントの長さを 7 ミルに短縮すると、遠端クロストークに対するギャップの影響を理解しやすくなります。

赤い曲線は立ち上がり時間が 7 ps の入力信号 (V20) を表し、シアンの曲線 (V8) は遠端での送信信号の波形を表し、水色 (V5) は近端のクロストークを表し、薄緑 ( V6) は遠端クロストークを表し、濃い緑色 (V15) は TL13 を通過した後のノード V44 での攻撃信号を表します。ギャップ部分の高インピーダンス特性により、この伝送線路セグメントでは反射の増加によるオーバーシュートが見られます。

オレンジ色の波形 (V13) は、V15 での攻撃信号の立ち上がりエッジと一致する、遠端の負のクロストーク パルスを示しています。近端クロストークも V15 での正の反射と一致します。攻撃信号がギャップを通過するときに遅延が発生すると、反射による追加の電圧スイングによって遠端クロストーク パルスの振幅が増加し、濃い緑色の波形に見られるように、その反転した形状が反射パルスの形状を反映します ( V14)、マゼンタの曲線 (V16) で示されているように、攻撃信号に結合し、結合セクションを離れるまで立ち上がり時間が減衰します。

この記事で扱う問題は、信号がセグメント化された平面を通過するときに、送信信号がインピーダンスの不整合により正と負の反射を受け、その反射時間はギャップを通過するのにかかる時間に等しいということです。これにより、信号と遠端クロストーク パルスの振幅が増加し、その結果、遠端クロストークの波形に比例して送信信号の立ち上がり時間が遅くなります。

分割された平面とエッジでの複数のリターン パスを考慮して、効果的なスロット アンテナが形成され、ノイズを外部に放射します。 EMI FCC クラス B 放射要件 (3 メートルのフィールド) を満たすには、放射ノイズは 100 ~ 30 MHz で 80 mV/m 未満、200 MHz ~ 216 GHz で 1 mV/m 未満である必要があります。

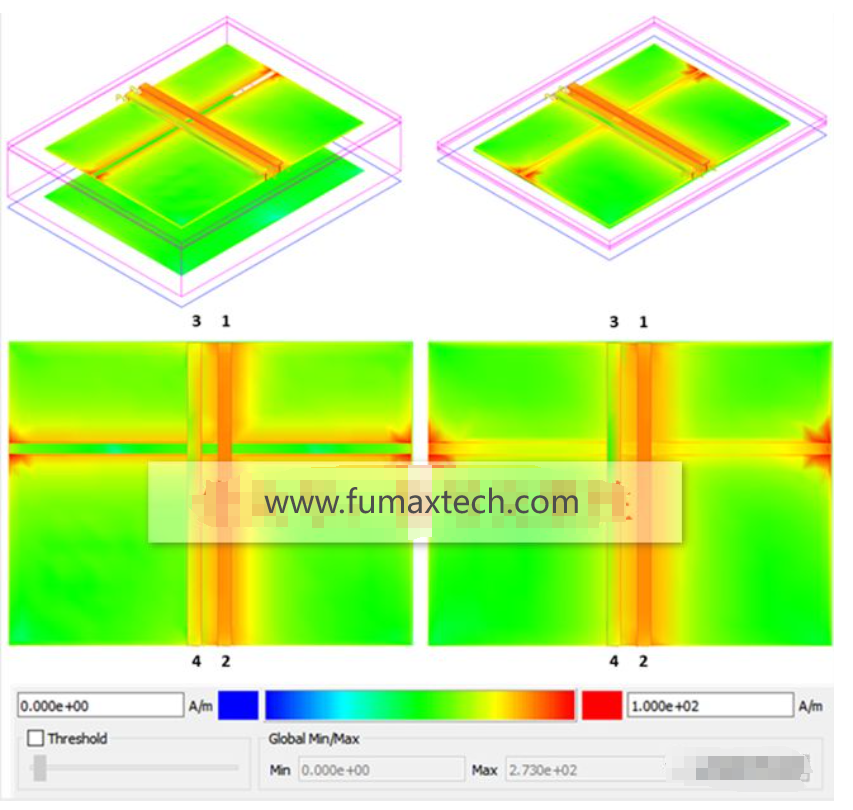

マイクロストリップ ラインがセグメント化されたプレーンを通過する場合、不連続なリターン パスやシールドの欠如により、ノイズが自由空間に放射される可能性があります。隣接する基準面間のギャップにおけるリターン電流密度の視覚化は、3D シミュレーション ソフトウェアによって実現できます。

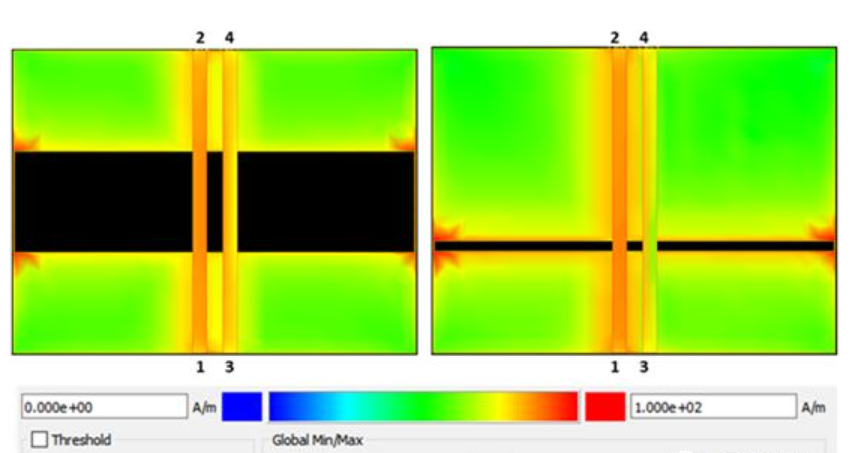

図 8 は、隣接するリファレンス プレーンのシングルエンド信号リターン電流密度を比較しています。左側では 4 GHz の正弦波が 50 ミルのギャップを通過し、右側では 5 ミルのギャップを通過します。 4 GHz 信号が選択されるのは、この信号が一般的な 8 層 PCIe ボード上の 3 Gbps PCIe Gen 4 のナイキスト周波数を表すためです。ポート 1 と 2 を適切に終端して信号をポート 3 からポート 4 に駆動することにより、セグメンテーションにおける基準面上のリターン電流密度の分布を明確に観察できます。

ビクティムラインが位置するギャップの端で電流密度がわずかに増加していることに注意してください。これは、前述したように、隣接するラインのリターン電流が追加の遠端クロストーク電圧を引き起こすことを示しています。この観点からすると、セグメンテーションを横切るシングルエンドのラインは最適なアプローチではない可能性があります。

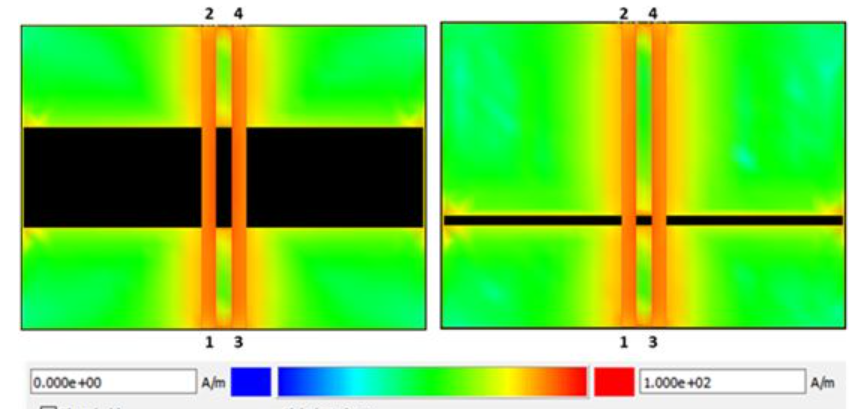

図 9 は、4 GHz の差動信号が 50 ミル (左) と 5 ミル (右) のギャップを通過するときのリファレンス プレーン上のリターン電流密度を示しています。 XNUMX つの差動ペア間の最大電流密度がセグメンテーションの端に集中しており、ギャップに沿って伝播するのはごく一部であることがわかります。

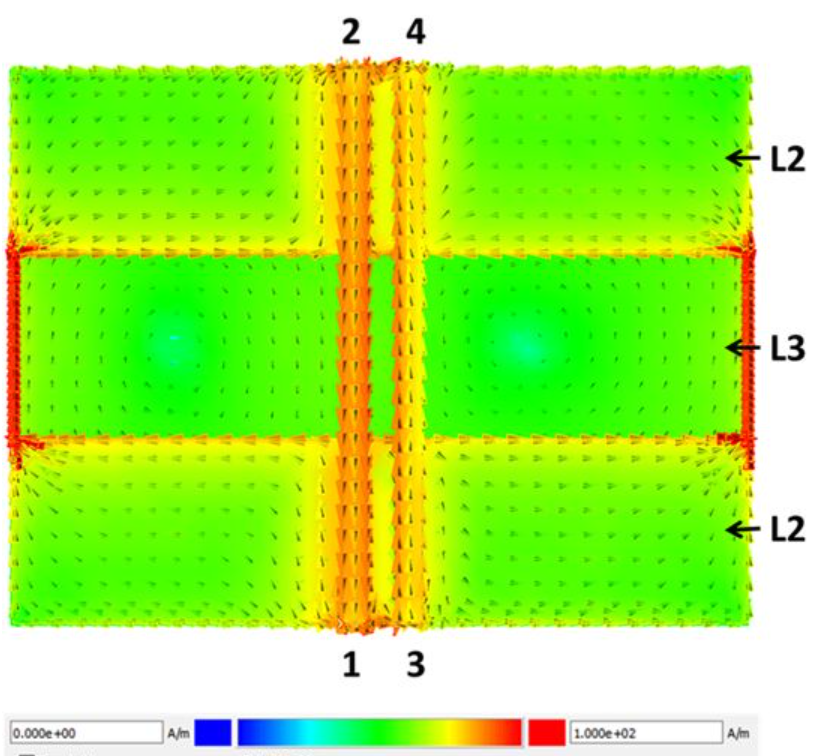

シングルエンド信号がポート 1 からポート 2 に入力され、他のポートが終端されている場合、図 10 はプレーン層 L2 および L3 上の電流の方向を示しています。電流の方向がポート 2 からポート 1 の場合、L2 のリターン電流はギャップの遠端 (ポート 1 側) で 3 つの部分に分割されることがわかります。さらに、L2 には 2 つの逆回転電流があり、主にギャップの左半分と右半分に集中しています。これらは、平面キャビティに EM エネルギーを注入する L3 のギャップの端に沿った逆回転電流によって引き起こされます。 LXNUMXとLXNUMXの回転電流の方向が逆であることに注目してください。

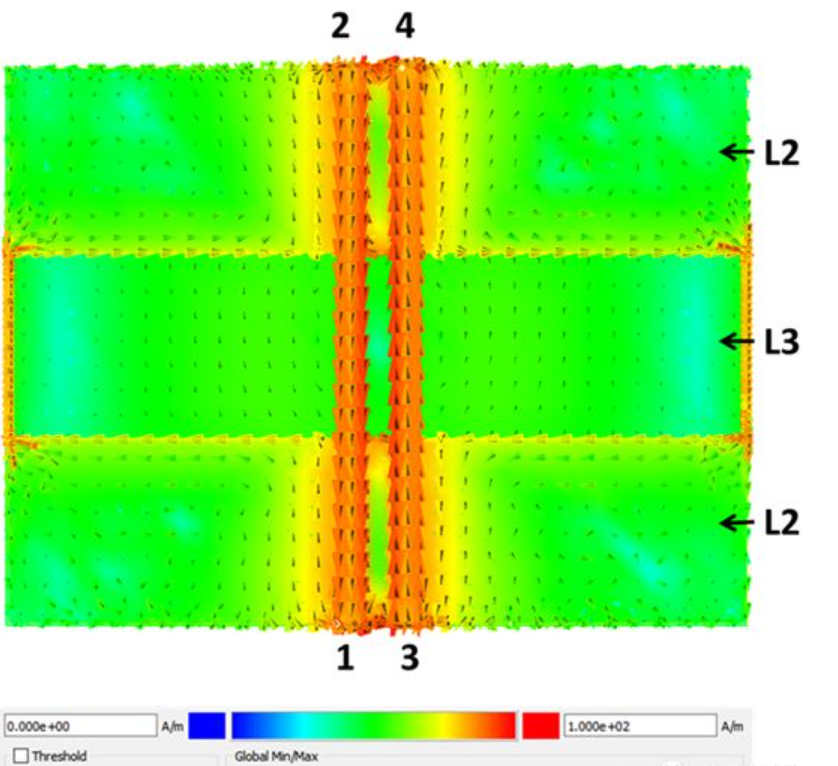

ただし、図 11 に示すように、差動信号が 3 つの伝送線に印加されると、ギャップの端に沿った電流の方向が同じであることが観察できます。 LXNUMX の回転電流は一方向であり、差動ペアとギャップの間に集中していることに注意することも重要です。ここでの問題は、差動信号が XNUMX つの伝送線に印加された場合でも、依然としてギャップの端に電流が流れ、平面空洞にノイズが導入され、自由空間に放射されて EMI が発生することです。

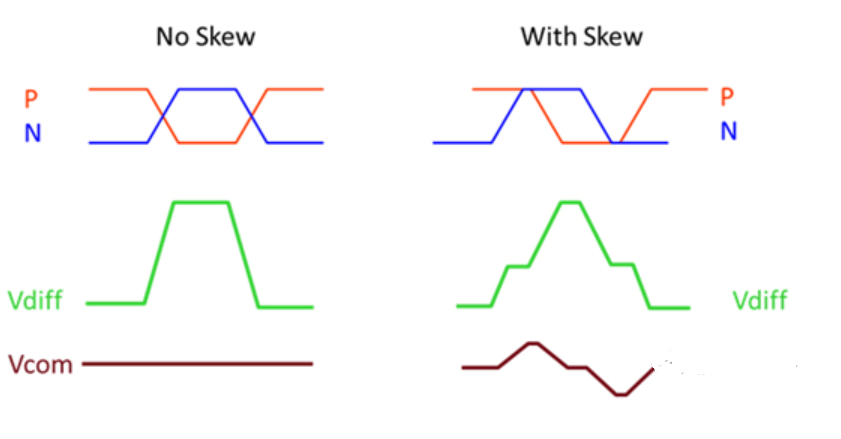

先ほどの解析では、差動ペアの例では完全な内部整合を想定していましたが、実際にはそのようなケースは稀です。不等な配線長、グラスファイバーの影響、コネクタピンの長さの違い、レイヤー変更時の差動ビアの非対称性などの要因により、内部遅延の不整合が発生する可能性があります。このような状況が発生すると、一部のコモンモード信号が差動モード信号に変換される可能性があります。図 12 に示すように、変換の程度は内部遅延の不一致によって異なります。理想的な差動ペアでは、Vdiff は P 信号と N 信号の間の電圧差を表します。位相差が 180 度の場合、コモンモード電圧は 180 倍になり、コモンモード電圧はなくなります。ただし、スキューがある場合、差動ペアの位相差は XNUMX 度ではなくなります。スキューを考慮すると、差動信号が変形し、その結果コモンモード電圧 (Vcom) が生じます。コモンモード電圧の大きさと形状は位相オフセットに比例します。 PとNの位相が同相の場合、差動電圧は存在せず、全て同相電圧となります。コモンモード電圧にはリターンパスも必要で、そのパスが遮断されると、そのリターン電流はシングルエンドリターン電流と同様にスプリットプレーンを通過します。

一部の PCIe 配線仕様によれば、最悪の場合のスキューは 0.21UI (3 UI は 8 ビットの時間を表します) です。 PCIe Gen0.21 26.3Gbps では、50UI オフセットは 13ps に相当します。図 8 に示すように、理想的な状況と比較すると、100mil ギャップを通過するシナリオは内部位相シフトに相当します。予想通り、コモンモード電圧はパーティションプレーンを通過し、コモンモードリターン電流はシングルエンド線路がパーティションプレーンを通過する場合の状況と同様です(図XNUMX)。唯一の違いは、XNUMX% のコモンモード電流は存在しないため、差動モードのリターン電流も存在することです。

対処すべき最後の問題は、隣接するグランド層と分割された電源層の間に非常に薄い誘電体層がある場合、それが分割層を通過するときにより良いリターンパスとして機能することです。論理的には、これは信号の完全性の観点からは理にかなっています。伝送線路と分割された基準面の間の誘電体の厚さが増加すると、伝送線路のインピーダンスが減少するからです。

前の例では、厚さ 62 ミルの 6 層基板を想定しました。これにより、スタック内層の誘電体の厚さがほぼ決まります。リファレンス プレーンを電源プレーン間のギャップに近づけるには、スタックの対称性と合計の厚さを維持するために PCB 層の数を少なくとも XNUMX 層に増やす必要があります。

ギャップの下の誘電体の厚さを減らし、5 ミルのギャップ、シングルエンドのケースを再シミュレーションした場合の結果を図 14 に示します。この薄い誘電体層は 2 ミルに設定されており、これはデカップリングの一般的な厚さです。電源プレーン上の埋め込み容量コア。図 5 に示すように、H1 の厚さ 1.2 ミルと電源プレーン L2 の厚さ 1 ミルを追加すると、ギャップの下の誘電体の厚さの合計は 8.2 ミルになります。

左の図では、リターン電流の大部分が基準面 L2 のギャップの周りにそらされていることがわかります。右の図では、信号がギャップを通過するときに、リターン電流の大部分は伝送線路の下の基準面 L3 に向かって流れますが、一部の電流はまだ L2 のギャップ付近に残り、それによってノイズが放射されます。

信号完全性の観点から、図 15 に示すように、反射信号と近端クロストーク ノイズは実質的に半分になりました。送信信号の立ち上がり時間の減衰が少なくなり、遠端クロストークも改善されました。 。

本題に戻りますが、どちらの見方が正しいのでしょうか?どちらも完全に正しいわけではありません。この記事では、スプリット プレーンを通過するマイクロストリップ ラインのいくつかのシナリオについて説明します。シグナルインテグリティの観点から、特定の条件下では、マイクロストリップラインがスプリットプレーンを通過することが許容される場合があります。たとえば、上記のシミュレーションでは、スプリット プレーン間のギャップが 5 ミルに減少し、隣接するプレーン層の間に薄い誘電体層が追加されている限り、クロストークは大幅に増加しません。実際のノイズ耐性によれば、これは影響を及ぼさない可能性があります。

ただし、EMC の観点から見ると、さらに多くのリスクと懸念があります。一部の戻り電流がスプリット プレーン ギャップの端に流れないというシナリオは決して存在しないため、EMI のリスクは依然として存在します。実際の設計では相互に関連する要素が多数あるため、ここやその他の状況に適用できる普遍的なルールを設けるのは困難です。

一般に、マイクロストリップ ラインはスプリット プレーンと交差しないようにする必要があります。ただし、実際のレイアウトと基板の積層の詳細な分析が不可能な場合は、外部シールドを追加するなど、ノイズ放射を軽減する代替方法が検討される場合があります。

結局のところ、この記事は、最新の高速設計では、シグナル インテグリティ、パワー インテグリティ、または EMC を個別に考慮することだけに限定することはできないことを強調します。 3 つすべてを同時に考慮する必要があります。 EMC を考慮せずに信号の完全性だけを考慮すると、誤った結論を導き出す可能性があり、最終製品の EMC 互換性テストで失敗する可能性があります。