Anmerkung des Herausgebers: In modernen Hochgeschwindigkeitsdesigns reicht es nicht aus, Signalintegrität, Leistungsintegrität und EMV separat zu analysieren; Für eine erfolgreiche Gestaltung ist ein ganzheitlicher Ansatz unerlässlich.

Hintergrundproblem: Wenn Signale Segmentierungsbereiche zwischen benachbarten Referenzebenen auf einer Ebene überqueren, kommt es häufig zu Diskussionen über die Signalintegrität. Einige argumentieren, dass Signale die Segmentierung nicht überschreiten sollten, da dies zu Übersprechen und EMV-Problemen führen könnte, während andere meinen, dass es bei sorgfältiger Gestaltung des Schichtaufbaus und der Breite der Segmentierungslücken auf Strom-/Masseebenen kein Problem geben sollte. Was ist also der richtige Ansatz? Die beste Antwort ist natürlich: „Es kommt darauf an!“ In diesem Artikel wird das Szenario untersucht, wenn Signale segmentierte Ebenen durchlaufen.

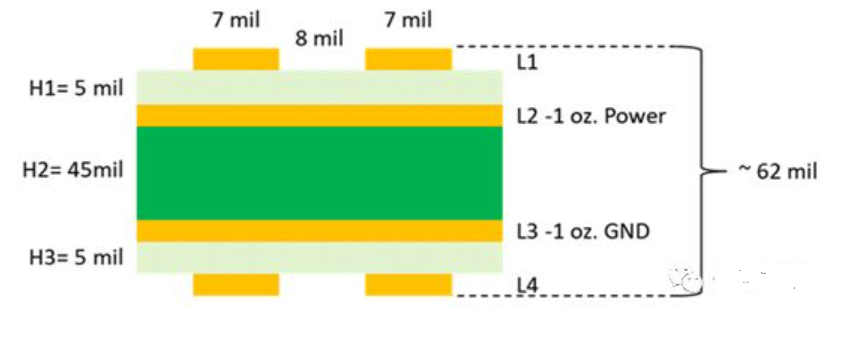

Betrachten wir zunächst einen typischen vierschichtige Leiterplatte Stapelung mit einer Gesamtdicke von 62 mil. Die Oberflächenschicht ist die Signalschicht, während die inneren Schichten die ebenen Schichten sind. Die Leiterbahnbreite beträgt 7/8 mil, mit einer Differenzimpedanz von 100 Ohm und einer Single-Ended-Impedanz von 56 Ohm.

Im modernen elektronischen Produktdesign ist es durchaus üblich, in einem Produkt mehrere Stromschienen zu haben, was bedeutet, dass die Stromebene in einer vierschichtigen Platine zwangsläufig geteilt wird. Daher ist das Vorhandensein von Signalkreuzungen über Teilungen beim Routing unvermeidbar.

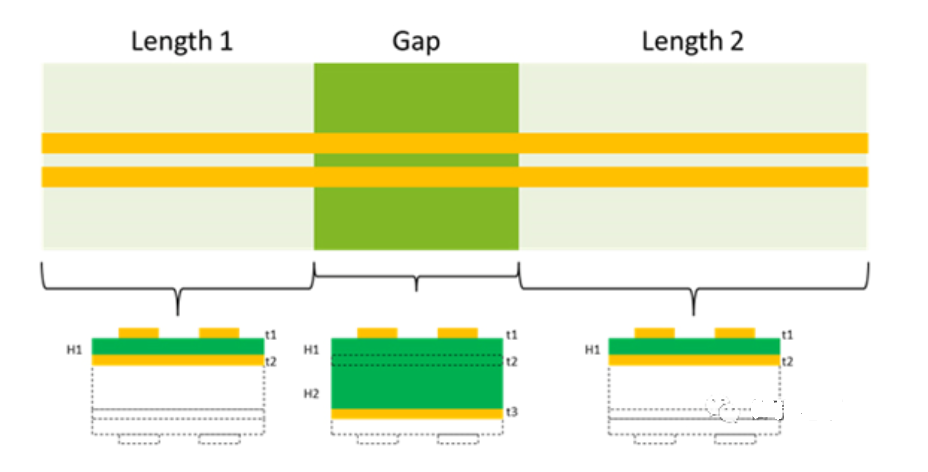

Unter der Annahme, dass ein Paar Oberflächenübertragungsleitungen einen 50 mil breiten Spalt zwischen benachbarten Schichten kreuzen, wie in der Abbildung gezeigt, wird der Querschnitt der Mikrostreifenleitung vor und nach dem Durchgang durch den Spalt dargestellt. Berücksichtigt wird die dielektrische Dicke H1 von der Oberfläche bis zur angrenzenden Leistungsreferenzschicht. Da es an der Lücke keine benachbarten Leistungsreferenzebenen gibt und die nächste Referenzebene der Boden neben der unteren Schicht ist, entspricht die Dielektrikumsdicke an der Lücke H1 plus der Dicke der 1-Unzen-Leistungsschicht plus der nächsten Dielektrikumsschicht H2. Wenn die Dicke der Leistungsschicht 1.2 mil beträgt, beträgt die gesamte dielektrische Dicke am Spalt 51.2 mil.

Die Näherung erster Ordnung dieser Topologie ist eine Kombination aus drei Segmenten von Übertragungsleitungen mit zwei unterschiedlichen Impedanzen. Das erste und das letzte Segment haben jeweils eine Differenzimpedanz von 100 Ohm und eine Single-Ended-Impedanz von 56 Ohm, während die Übertragungsleitung im Lückenteil eine Differenzimpedanz von 134 Ohm und eine Single-Ended-Impedanz von 103 Ohm aufweist. Seine Impedanz ist höher als bei anderen Teilen, was hier zu Signalreflexionen führt. Die Höhe und Breite der Reflexion sind Funktionen der entsprechenden Signalanstiegszeit und Lückengeometrie. Je schneller die Anstiegszeit und je größer der Spalt, desto stärker ist die verursachte Reflexion. Abbildung 3 zeigt die Simulationsergebnisse.

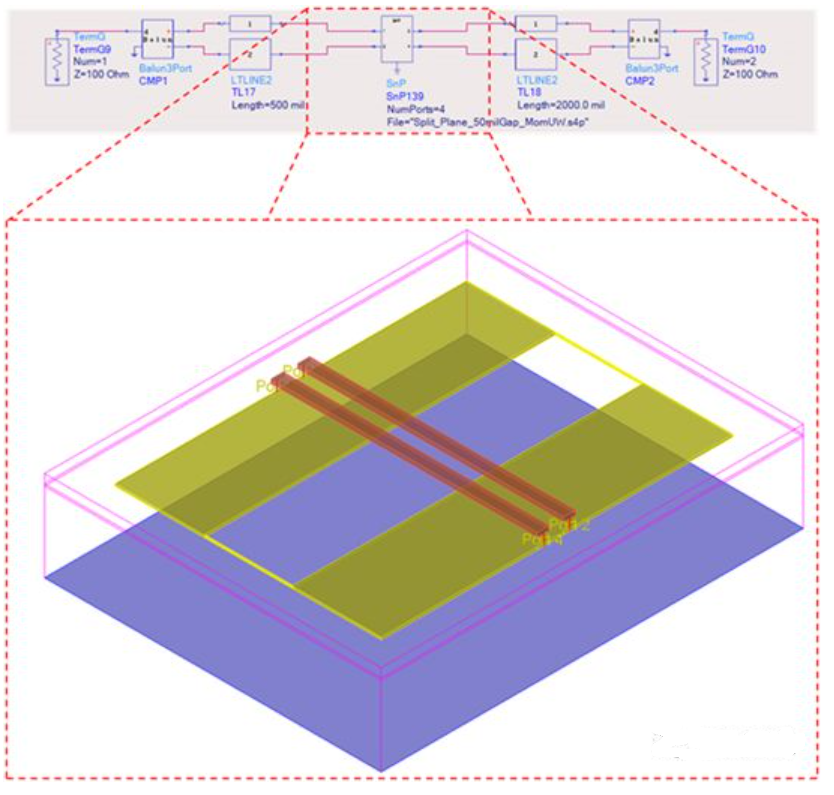

Das erste und dritte Segment der Übertragungsleitungen werden mit dem 2D-Modell von TLines-LineType (ADS) simuliert, während die Übertragungsleitung an der Lücke mit einem 3D-Löser für elektromagnetische Felder (Momentum oder EMPro) simuliert wird, um die elektromagnetischen Feldeffekte zu erhalten, wenn die Signal geht durch. Die dielektrischen Materialien sind die gleichen. S-Parameter werden extrahiert und im Schaltplan verwendet.

Die Gesamtlänge der Topologie beträgt 2.65 Zoll, wobei die Länge des ersten Segments der Übertragungsleitung (L1) 500 mil und die Länge des dritten Segments (L2) 2 Zoll beträgt. Der 3D-Teil ist in drei Segmente von jeweils 50 mil unterteilt, um die Anpassung der Spaltbreite zu erleichtern und gleichzeitig sicherzustellen, dass die Gesamtlänge unverändert bleibt.

Zum Vergleich der Auswirkungen der Spaltgröße werden zwei Spaltbreiten verwendet. Eine Lücke von 50 mil zwischen den Antriebsebenen ist üblich und stellt das Worst-Case-Szenario dar. Ein Abstand von 5 mil ist das optimale Szenario und stellt auch den typischen Mindestwert von der Übertragungsleitung bis zum Lötpad dar.

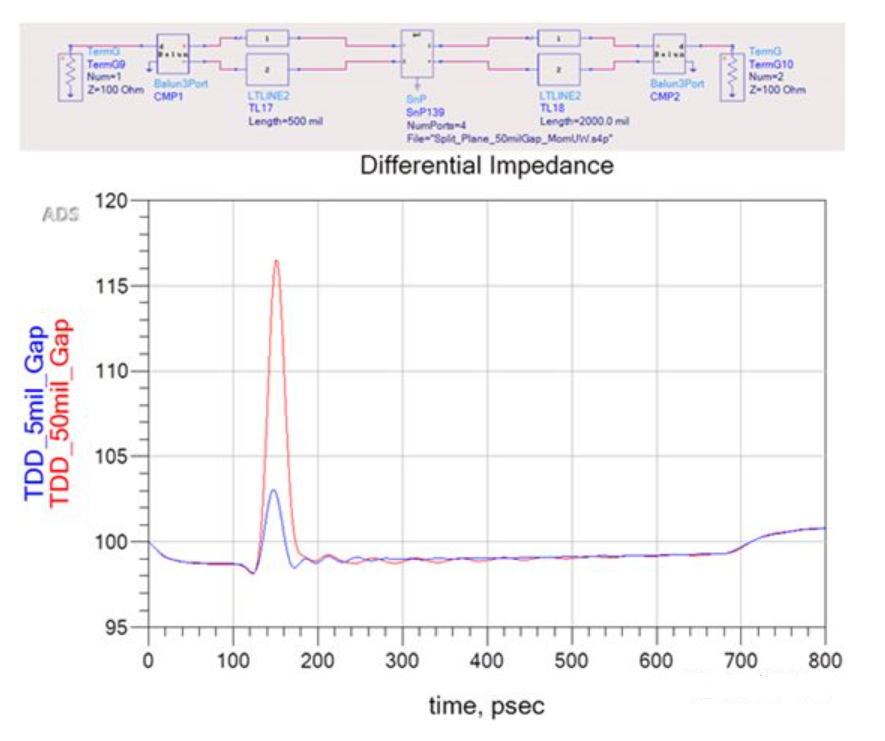

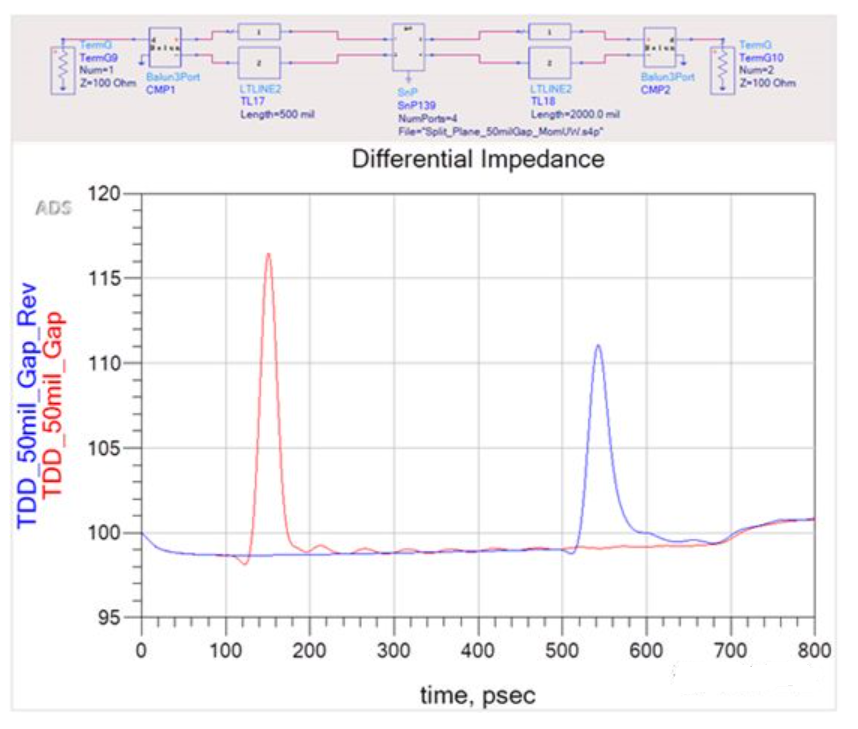

An Anschluss 1 wird eine differenzielle Erregerquelle angelegt, und der Vergleich der Differenzimpedanzen ist in Abbildung 4 dargestellt. Um die Anzeige der Impedanz an Anschluss 2 zu erleichtern, wird ein Balun-Wandler verwendet, um Anschluss 4 in Anschluss 2 umzuwandeln. Die rote Kurve stellt die Ergebnisse dar für einen Spalt von 50 mil, der im Vergleich zu den Ergebnissen für einen Spalt von 5 mil (blaue Kurve) eine höhere Impedanzdiskontinuität aufweist. Dies liegt daran, dass die Höhe des ausgesendeten Impulses sowohl durch die Anstiegszeit als auch durch die Spaltbreite bestimmt wird. Da die Anstiegszeit in ihrer räumlichen Länge im Vergleich zur Spaltbreite kleiner ist, kann durch eine alleinige Änderung der Anstiegszeit nicht die maximale Impedanzdiskontinuität erreicht werden. Dies wird unten durch eine Simulation demonstriert.

An Anschluss 2 wird eine Anregungsquelle mit einem Abstand von 50 mil angelegt und mit dem Eingangssignal von Anschluss 1 verglichen, wie in der folgenden Abbildung dargestellt. Aufgrund einer Verzögerung von 2.05 Zoll vor der Lücke und Verlusten in der Übertragungsleitung ist die Signalflanke langsamer. Wie erwartet ist die Amplitude der Reflexion tatsächlich geringer.

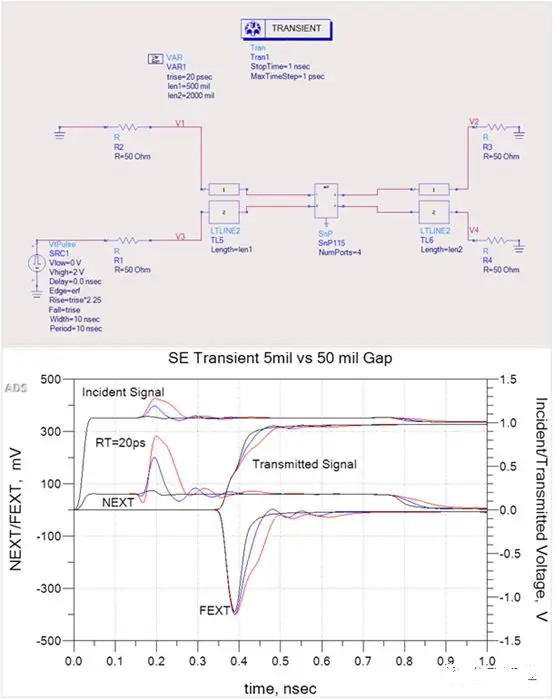

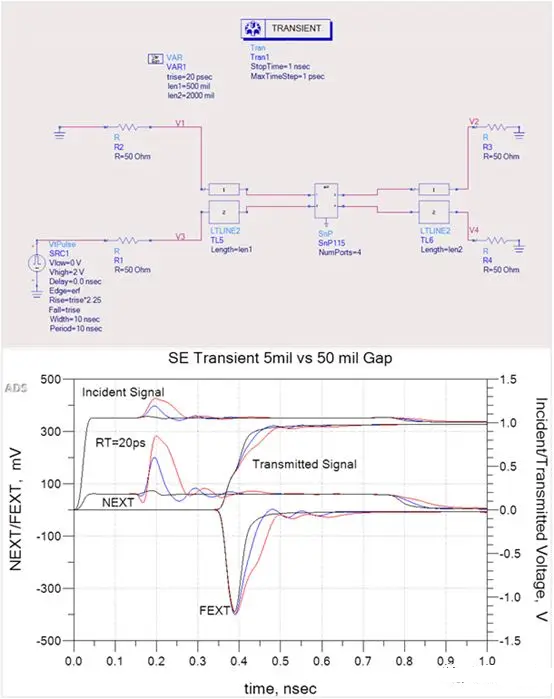

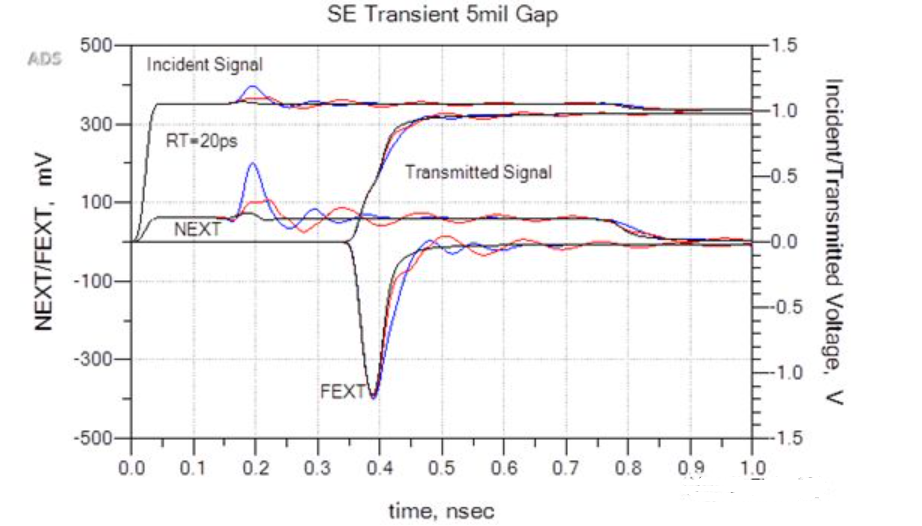

Hier ist die Analyse des Single-Ended-Falls, wie in der Abbildung dargestellt. Die rote Kurve stellt eine Lücke von 50 mil dar, die blaue Kurve stellt eine Lücke von 5 mil dar und die schwarze Kurve stellt keine Lücke dar. Bei einer Anstiegszeit von 20 ps ist die Reflexionsspannung am höchsten, wenn die Lücke 50 mil beträgt, was zu einem leichten Anstieg der Übertragungsleitungsverzögerung im Vergleich zum Fall ohne Lücke führt.

In allen drei Szenarien können typische Variationen der Nebensprechkurven am nahen Ende und am fernen Ende beobachtet werden. Die enge Kopplung zwischen den Übertragungsleitungen durch die Lücke führt zu höheren Reflexionen und damit zu stärkerem Nahnebensprechen.

Hier ist die Analyse des Single-Ended-Falls, wie in der Abbildung dargestellt. Die rote Kurve stellt eine Lücke von 50 mil dar, die blaue Kurve stellt eine Lücke von 5 mil dar und die schwarze Kurve stellt keine Lücke dar. Bei einer Anstiegszeit von 20 ps ist die Reflexionsspannung am höchsten, wenn die Lücke 50 mil beträgt, was zu einem leichten Anstieg der Übertragungsleitungsverzögerung im Vergleich zum Fall ohne Lücke führt.

In allen drei Szenarien können typische Variationen der Nebensprechkurven am nahen Ende und am fernen Ende beobachtet werden. Beim Durchgang durch die Lücke führt die enge Kopplung zwischen den Übertragungsleitungen zu höheren Reflexionen, was zu einem stärkeren Nahnebensprechen führt.

Bei einer Lücke von 50 mil nehmen die Nebensprechimpulse am nahen Ende deutlich zu, während das Nebensprechen am fernen Ende nur geringfügig zunimmt. Im Gegensatz zur Nahnebensprechspannung variiert der Spitzenwert der Fernnebensprechspannung mit der Kopplungslänge. Bei einer bestimmten Zeitverzögerung (TD) erreicht seine Amplitude ihren Höhepunkt bei etwa 50 % der Anstiegszeit des angreifenden Leitungssignals.

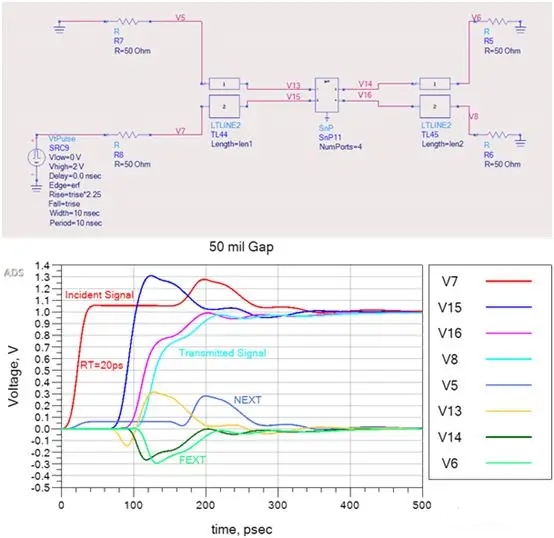

In ähnlicher Weise koppelt das Signal von der angreifenden Leitung an die Übersprechspannung am fernen Ende, die wiederum an die angreifende Leitung koppelt, was sich auf die Anstiegszeit auswirkt. Die Wellenform am anderen Ende der angreifenden Leitung ist die Überlagerung der Übersprechspannung am fernen Ende und der ursprünglichen Signalspannung, was zu keinem Übersprechen führt. Da das ferne Ende 2.65 Zoll vom Quellenende entfernt ist, nähert sich das Übersprechen am fernen Ende der Sättigung. Die Reduzierung der Länge des letzten Segments der Übertragungsleitung auf 100 mil, wie in Abbildung 7 dargestellt, erleichtert das Verständnis der Auswirkung der Lücke auf das Nebensprechen am fernen Ende.

Die rote Kurve stellt das Eingangssignal (V7) mit einer Anstiegszeit von 20 ps dar, die cyanfarbene Kurve (V8) stellt die Wellenform des übertragenen Signals am fernen Ende dar, hellblau (V5) stellt Nebensprechen am nahen Ende dar, hellgrün ( V6) stellt Übersprechen am fernen Ende dar und dunkelgrün (V15) stellt das Angriffssignal am Knoten V13 nach Durchlaufen von TL44 dar. Aufgrund der hohen Impedanzeigenschaften im Lückenabschnitt sind in diesem Übertragungsleitungsabschnitt Überschwingungen aufgrund erhöhter Reflexionen zu beobachten.

Die orangefarbene Wellenform (V13) zeigt negative Übersprechimpulse am fernen Ende, die mit der ansteigenden Flanke des Angriffssignals bei V15 übereinstimmen. Auch Nahnebensprechen stimmt mit der positiven Reflexion bei V15 überein. Da das angreifende Signal beim Durchgang durch die Lücke eine Verzögerung erfährt, erhöht der zusätzliche Spannungshub der Reflexion die Amplitude der Übersprechimpulse am fernen Ende, und seine invertierte Form spiegelt die Form des reflektierten Impulses wider, wie in der dunkelgrünen Wellenform zu sehen ist ( V14), der dann wieder an das Angriffssignal koppelt und die Anstiegszeit abklingen lässt, bis er den Kopplungsabschnitt verlässt, wie die magentafarbene Kurve (V16) zeigt.

Das in diesem Artikel angesprochene Problem besteht darin, dass beim Durchgang eines Signals durch eine segmentierte Ebene das übertragene Signal aufgrund von Impedanzfehlanpassungen positive und negative Reflexionen erfährt, wobei die Reflexionszeit der Zeit entspricht, die für den Durchgang durch die Lücke benötigt wird. Dadurch wird die Amplitude des Signals und der Nebensprechimpulse am fernen Ende erhöht, wodurch die Anstiegszeit des übertragenen Signals proportional zur Wellenform des Nebensprechens am fernen Ende verlangsamt wird.

Unter Berücksichtigung mehrerer Rückwege an der segmentierten Ebene und an den Kanten entsteht eine effektive Schlitzantenne, die Rauschen nach außen abstrahlt. Um die Strahlungsanforderungen der EMI FCC Klasse B (3-Meter-Feld) zu erfüllen, muss das abgestrahlte Rauschen zwischen 100 und 30 MHz weniger als 80 mV/m und zwischen 200 MHz und 216 GHz weniger als 1 mV/m betragen.

Wenn Mikrostreifenleitungen durch segmentierte Ebenen verlaufen, kann aufgrund diskontinuierlicher Rückwege und fehlender Abschirmung Rauschen in den freien Raum abstrahlen. Die Visualisierung der Rückstromdichte an der Lücke zwischen benachbarten Referenzebenen kann durch 3D-Simulationssoftware erreicht werden.

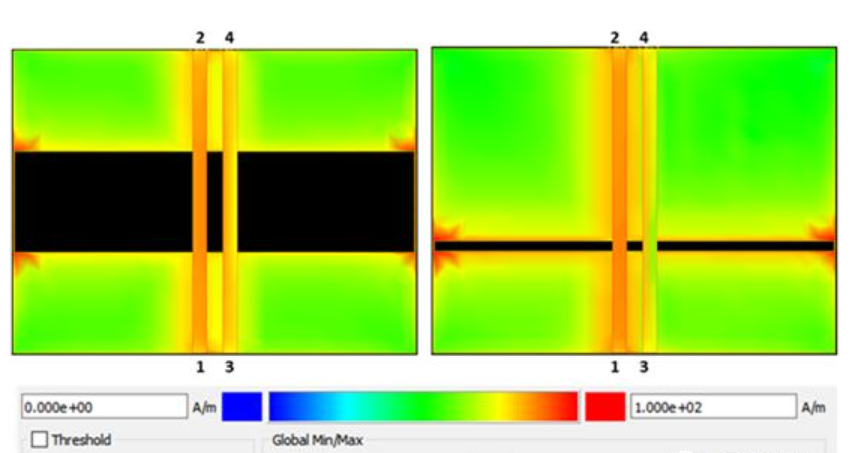

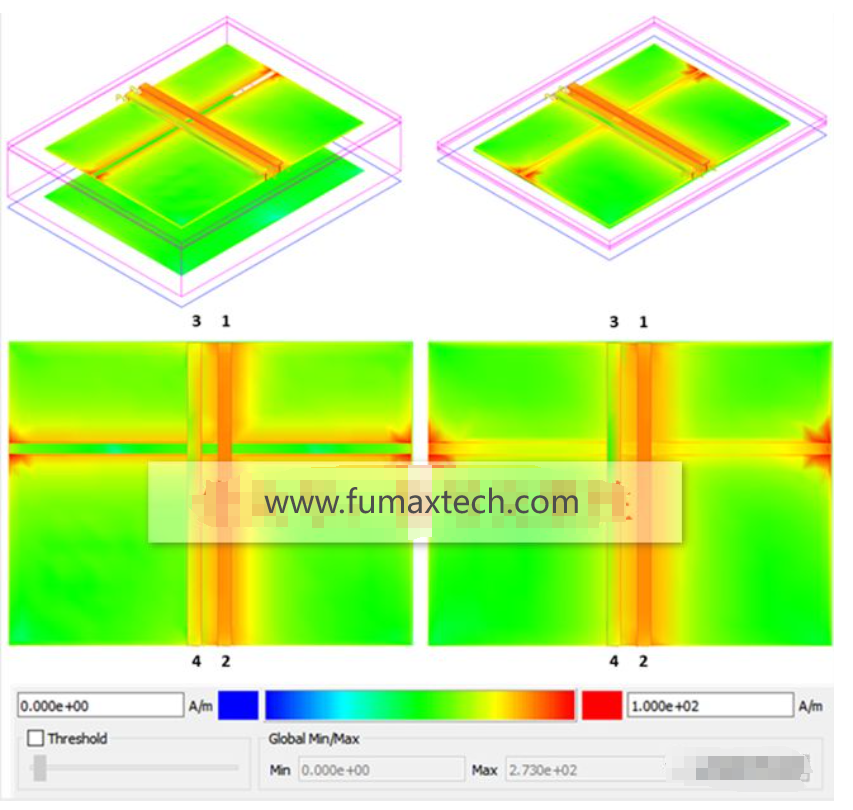

Abbildung 8 vergleicht die Rückstromdichte des Single-Ended-Signals auf benachbarten Referenzebenen. Auf der linken Seite verläuft eine 4-GHz-Sinuswelle durch eine 50-mil-Lücke, während sie rechts durch eine 5-mil-Lücke verläuft. Die Wahl eines 4-GHz-Signals liegt daran, dass es die Nyquist-Frequenz von 8 Gbit/s PCIe Gen 3 auf einer typischen 4-Layer-PCIe-Karte darstellt. Indem das Signal von Anschluss 1 zu Anschluss 2 geleitet wird und die Anschlüsse 3 und 4 ordnungsgemäß abgeschlossen sind, kann die Verteilung der Rückstromdichte auf der Referenzebene an der Segmentierung deutlich beobachtet werden.

Beachten Sie den leichten Anstieg der Stromdichte an den Rändern der Lücke, wo sich die Opferleitung befindet. Dies weist darauf hin, dass der Rückstrom auf benachbarten Leitungen eine zusätzliche Übersprechspannung am fernen Ende verursacht, wie bereits erläutert. Aus dieser Perspektive sind Single-Ended-Linien, die die Segmentierung kreuzen, möglicherweise kein optimaler Ansatz.

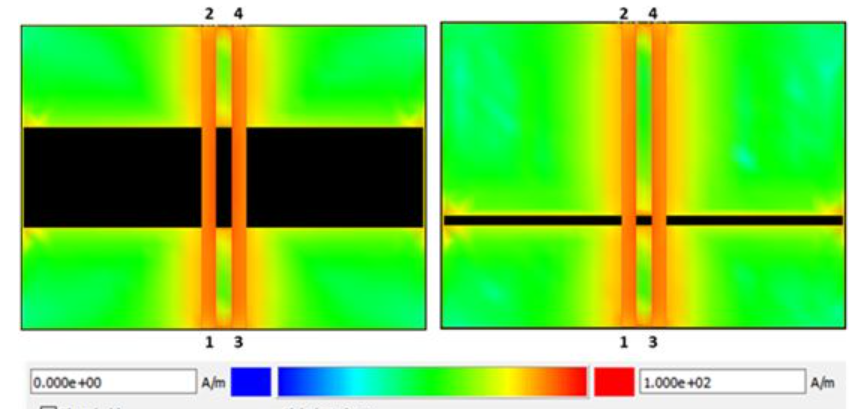

Abbildung 9 zeigt die Rückstromdichte auf der Referenzebene, wenn ein 4-GHz-Differenzsignal Lücken von 50 mil (links) und 5 mil (rechts) durchläuft. Es ist zu beobachten, dass die maximale Stromdichte zwischen den beiden Differentialpaaren an den Rändern der Segmentierung konzentriert ist und sich nur ein kleiner Teil entlang der Lücke ausbreitet.

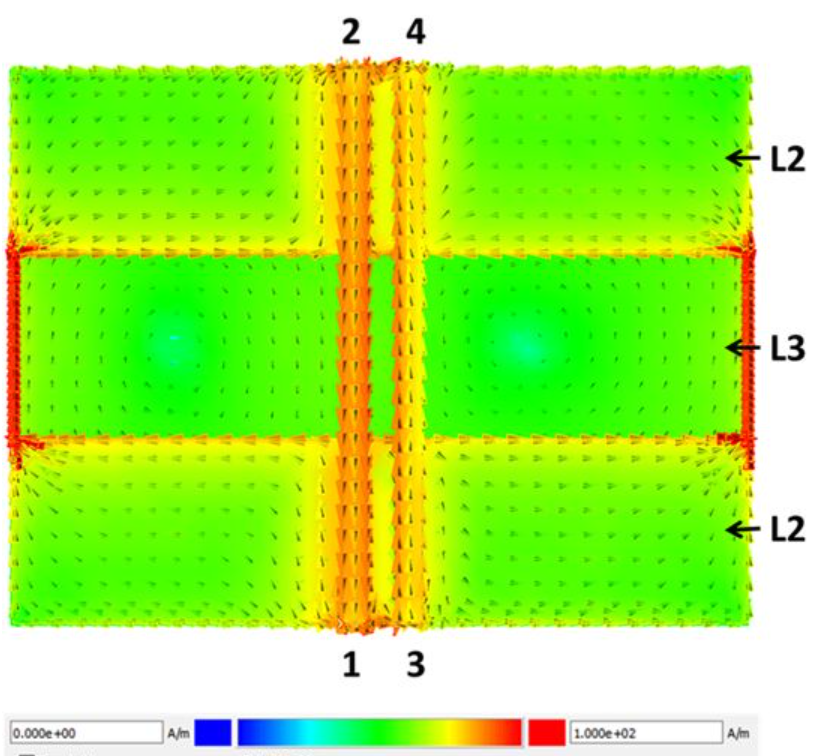

Wenn ein Single-Ended-Signal von Port 1 zu Port 2 eingegeben wird und die anderen Ports terminiert sind, zeigt Abbildung 10 die Richtung der Ströme auf den Ebenen L2 und L3. Es ist zu beobachten, dass, wenn die Stromrichtung von Anschluss 2 zu Anschluss 1 verläuft, der Rückstrom auf L2 am anderen Ende der Lücke (Seite von Anschluss 1) in zwei Teile aufgeteilt wird. Darüber hinaus gibt es auf L3 zwei umgekehrt rotierende Ströme, die sich hauptsächlich auf die linke und rechte Hälfte der Lücke konzentrieren. Diese werden durch umgekehrt rotierende Ströme entlang der Lückenkante auf L2 verursacht, die EM-Energie in den ebenen Hohlraum injizieren. Bemerkenswert ist, dass die Richtung der Drehströme auf L2 und L3 entgegengesetzt ist.

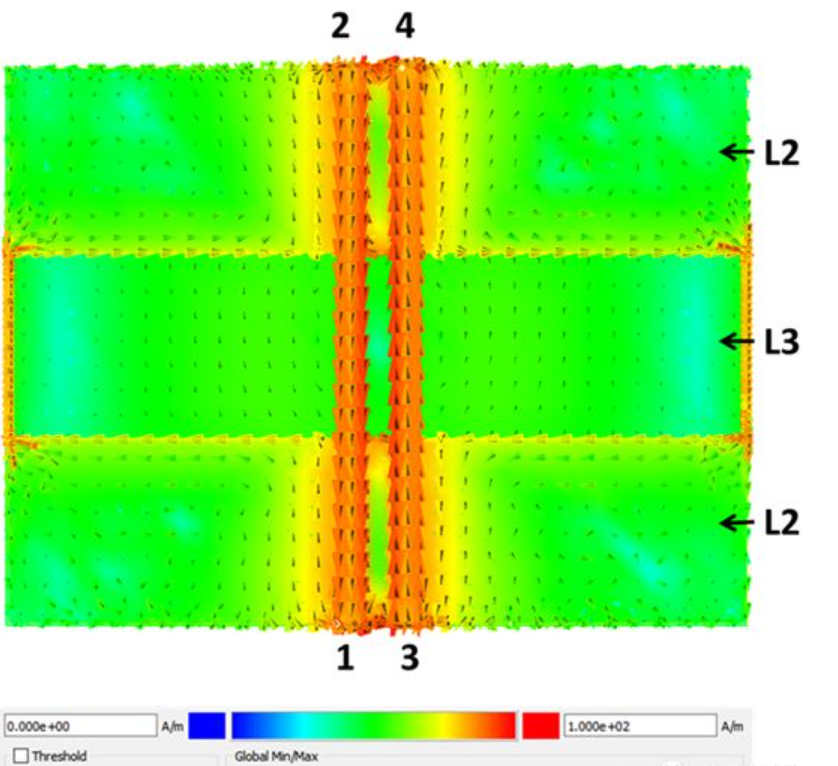

Wenn jedoch ein Differenzsignal an die beiden Übertragungsleitungen angelegt wird, wie in Abbildung 11 dargestellt, kann beobachtet werden, dass die Richtung des Stroms entlang der Kante der Lücke dieselbe ist. Es ist auch wichtig zu beachten, dass der rotierende Strom auf L3 unidirektional ist und sich zwischen den Differentialpaaren und der Lücke konzentriert. Das Problem hierbei ist, dass selbst wenn ein Differenzsignal an die beiden Übertragungsleitungen angelegt wird, immer noch Strom zum Rand des Spalts fließt, wodurch Rauschen in den ebenen Hohlraum eindringt und in den freien Raum abstrahlt, was zu elektromagnetischen Störungen führt.

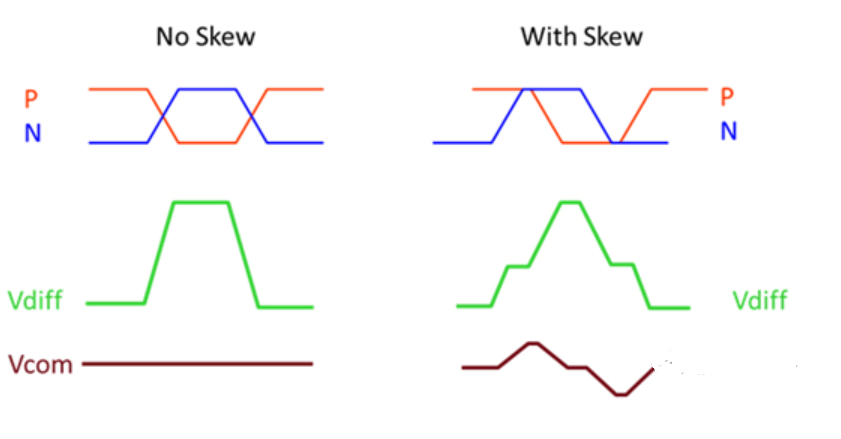

In der vorherigen Analyse wurde am Beispiel eines Differentialpaars von einer perfekten internen Übereinstimmung ausgegangen, aber in Wirklichkeit sind solche Fälle selten. Faktoren wie ungleiche Routing-Längen, Glasfasereffekte, unterschiedliche Längen der Steckerstifte oder Asymmetrie in den Differential-Durchkontaktierungen beim Lagenwechsel können zu internen Verzögerungsfehlanpassungen führen. Wenn diese Situationen auftreten, können einige Gleichtaktsignale in Gegentaktsignale umgewandelt werden. Wie in Abbildung 12 dargestellt, hängt der Grad der Konvertierung von der internen Verzögerungsfehlanpassung ab. In einem idealen Differentialpaar stellt Vdiff die Spannungsdifferenz zwischen P- und N-Signalen dar. Wenn ihre Phasendifferenz 180 Grad beträgt, verdoppelt sich die Gleichtaktspannung und es liegt keine Gleichtaktspannung vor. Wenn jedoch ein Versatz vorliegt, beträgt die Phasendifferenz des Differentialpaars nicht 180 Grad. Unter Berücksichtigung des Zeitversatzes verformt sich das Differenzsignal, was zu einer Gleichtaktspannung (Vcom) führt. Größe und Form der Gleichtaktspannung sind proportional zum Phasenversatz. Wenn die Phasen von P und N identisch sind, gibt es keine Differenzspannung und alles wird zur Gleichtaktspannung. Die Gleichtaktspannung erfordert auch einen Rückweg, und wenn der Weg unterbrochen wird, fließt sein Rückstrom ähnlich wie Single-Ended-Rückströme durch die geteilte Ebene.

Gemäß einigen PCIe-Verkabelungsspezifikationen beträgt der ungünstigste Versatz 0.21 UI (ein UI repräsentiert die Zeit eines Bits). Bei PCIe Gen3 8 Gbit/s entspricht ein Offset von 0.21 UI 26.3 ps. Das Szenario, in dem eine Lücke von 50 mil durchlaufen wird, entspricht einer internen Phasenverschiebung, wie in Abbildung 13 dargestellt, im Vergleich zur Idealsituation. Wie erwartet fließt die Gleichtaktspannung durch die Trennebene, und der Gleichtakt-Rückstrom ähnelt der Situation bei Single-Ended-Leitungen, die durch die Trennebene verlaufen (Abbildung 8). Der einzige Unterschied besteht darin, dass es keinen 100-prozentigen Gleichtaktstrom gibt, es also auch einen Gegenstrom-Rückstrom gibt.

Das letzte zu lösende Problem besteht darin, dass eine extrem dünne dielektrische Schicht zwischen der angrenzenden Erdungsschicht und der unterteilten Leistungsschicht als besserer Rückweg dient, wenn sie durch die unterteilte Schicht verläuft. Aus Sicht der Signalintegrität ist dies logischerweise sinnvoll, da die Impedanz von Übertragungsleitungen mit zunehmender Dielektrikumsdicke zwischen der Übertragungsleitung und der unterteilten Referenzebene abnimmt.

In den vorherigen Beispielen sind wir von einer vierschichtigen Platte mit einer Dicke von 62 mil ausgegangen. Dies bestimmt nahezu die Dicke der inneren Dielektrikumschicht im Stapel. Um die Referenzebene näher an die Lücke zwischen den Leistungsebenen zu bringen, muss die Anzahl der PCB-Schichten auf mindestens 6 Schichten erhöht werden, um die Stapelsymmetrie und Gesamtdicke aufrechtzuerhalten.

Wenn die Dicke des Dielektrikums unterhalb des Spalts verringert wird, um den Single-Ended-Fall mit einem Spalt von 5 mil neu zu simulieren, sind die Ergebnisse in Abbildung 14 dargestellt. Diese dünne dielektrische Schicht ist auf 2 mil eingestellt, was eine übliche Dicke für die Entkopplung ist vergrabene Kapazitätskerne auf der Leistungsebene. Addiert man die Dicke von 5 mil für H1 und 1.2 mil für die Leistungsebene L2, wie in Abbildung 1 dargestellt, beträgt die Gesamtdicke des Dielektrikums unterhalb des Spalts 8.2 mil.

Im linken Bild ist zu sehen, dass der größte Teil des Rückstroms um die Lücke in der Referenzebene L2 herumgeleitet wird. Wenn das Signal im rechten Bild die Lücke passiert, fließt der größte Teil des Rückstroms zur Referenzebene L3 unterhalb der Übertragungsleitung, aber ein Teil des Stroms verbleibt immer noch in der Nähe der Lücke in L2, wodurch etwas Rauschen abgestrahlt wird.

Aus Sicht der Signalintegrität wurden die reflektierten Signale und das Nebensprechrauschen am nahen Ende im Wesentlichen halbiert, wie in Abbildung 15 dargestellt. Die Anstiegszeit des übertragenen Signals wird weniger gedämpft und auch das Nebensprechen am fernen Ende wurde verbessert .

Zurück zur Hauptfrage: Welche Perspektive ist richtig? Beides ist nicht ganz richtig. In diesem Artikel werden mehrere Szenarien von Mikrostreifenleitungen diskutiert, die durch geteilte Ebenen verlaufen. Aus Sicht der Signalintegrität kann es unter bestimmten Bedingungen akzeptabel sein, dass Mikrostreifenleitungen durch geteilte Ebenen verlaufen. Solange beispielsweise in der obigen Simulation der Spalt zwischen geteilten Ebenen auf 5 mil reduziert wird und eine dünne dielektrische Schicht zwischen benachbarten Ebenenschichten hinzugefügt wird, nimmt das Übersprechen nicht wesentlich zu. Gemäß den tatsächlichen Lärmtoleranzen hat dies möglicherweise keine Auswirkungen.

Aus EMV-Sicht bestehen jedoch noch weitere Risiken und Bedenken. Es gibt nie ein Szenario, in dem ein Teil des zurückfließenden Stroms niemals bis zum Rand der Split-Plane-Lücke fließt, daher besteht immer noch die Gefahr von elektromagnetischen Störungen. Aufgrund der Vielzahl miteinander verbundener Faktoren in tatsächlichen Designs ist es schwierig, eine universelle Regel zu finden, die hier oder in jeder anderen Situation anwendbar ist.

Im Allgemeinen sollten Mikrostreifenleitungen das Kreuzen geteilter Ebenen vermeiden. Wenn jedoch eine detaillierte Analyse des tatsächlichen Layouts und des Platinenaufbaus nicht möglich ist, können alternative Methoden zur Minderung der Lärmstrahlung untersucht werden, beispielsweise das Hinzufügen zusätzlicher externer Abschirmung.

Letztendlich wird in diesem Artikel betont, dass wir uns bei modernen Hochgeschwindigkeitsdesigns nicht darauf beschränken können, nur die Signalintegrität, die Leistungsintegrität oder die EMV einzeln zu betrachten. Alle drei müssen gleichzeitig berücksichtigt werden. Wenn wir nur die Signalintegrität ohne EMV-Überlegungen berücksichtigen, können wir falsche Schlussfolgerungen ziehen, die möglicherweise zu Fehlern bei der EMV-Kompatibilitätsprüfung des Endprodukts führen.